# Digital Signal Processing IC Handbook

GEC PLESSEY

# DIGITAL SIGNAL PROCESSING

**IC Handbook**

GEC PLESSEY

S E M I C O N D U C T O R S

# Foreword

In 1988, the first family of Plessey Digital Signal Processing building block components was launched, offering a significant increase in integration over the traditional Multipliers, ALUs and Address Generators.

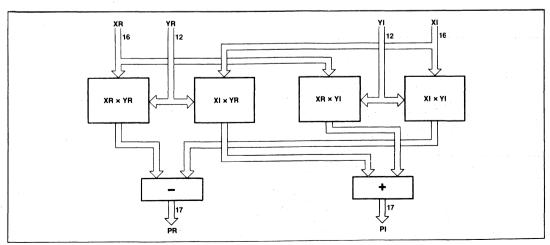

Despite the fact that the data in almost all DSP applications is complex-valued (that is, of the form A+jB), the hardware of current DSP processors is only capable of operation on real data.

The GEC Plessey Semiconductors PDSP building block family is the only chip set to offer Complex Arithmetic as standard. This provides the system designer with four-fold improvements in speed and substantial reduction in board area and power consumption.

More recently, GEC Plessey Semiconductors has launched a new range of Algorithm Specific DSP devices. These components are dedicated high performance (sampling rates up to 40MHz) solutions to common DSP algorithms such as FIR Filtering, Co-ordinate Conversion, Fast Fourier Transforms and 2D Convolution.

The high level of functional integration offered by the Algorithm Specific components allows high performance DSP functions to be implemented with reduced component count and improved power consumption.

The application areas addressed by the PDSP family (building block and application specific) include:

Digital filtering

Pulse compression

Digital modulation/demodulation

Correlation

Convolution

Image processing

Digital waveform synthesis

| Contents                                                    | PAGE |

|-------------------------------------------------------------|------|

| Foreword                                                    | 2    |

| Product index                                               | 4    |

| Product list – alphanumeric                                 | 5    |

| Technical data                                              | 7    |

| Application notes                                           |      |

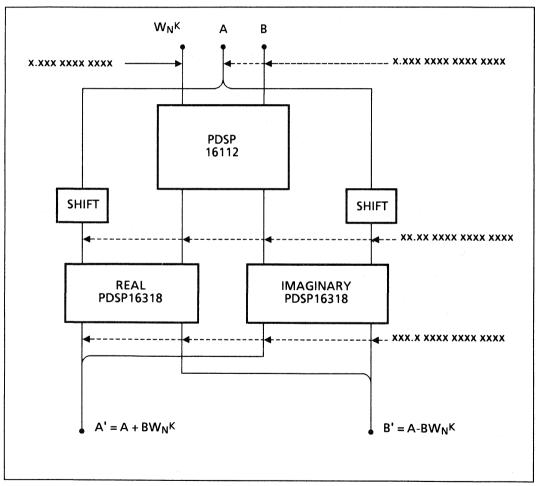

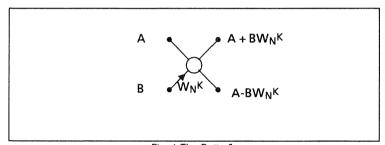

| A 50ns Butterfly processor                                  | 163  |

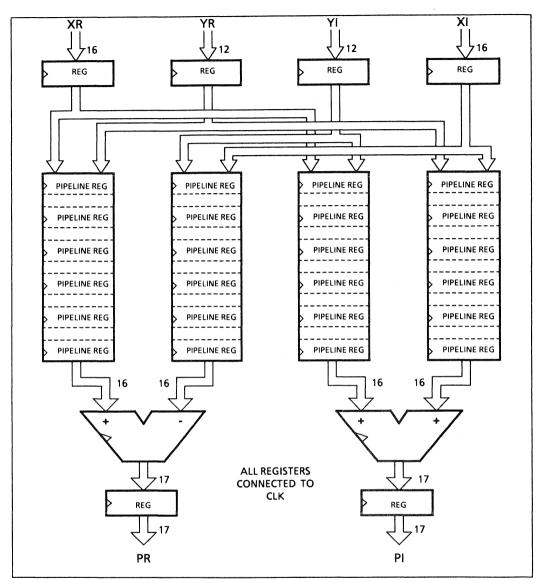

| A 50ns complex multiplier/accumulator                       | 165  |

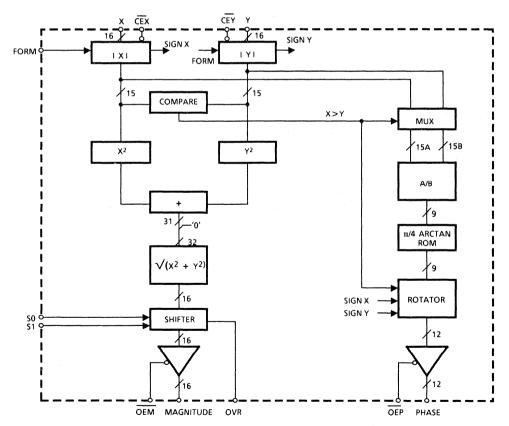

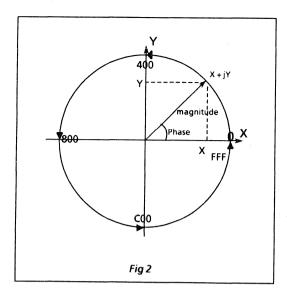

| The Pythagoras processor                                    | 167  |

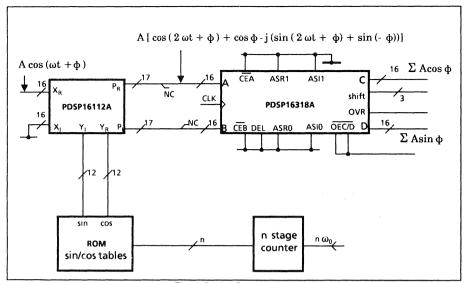

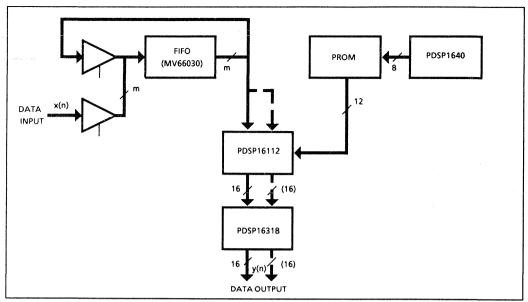

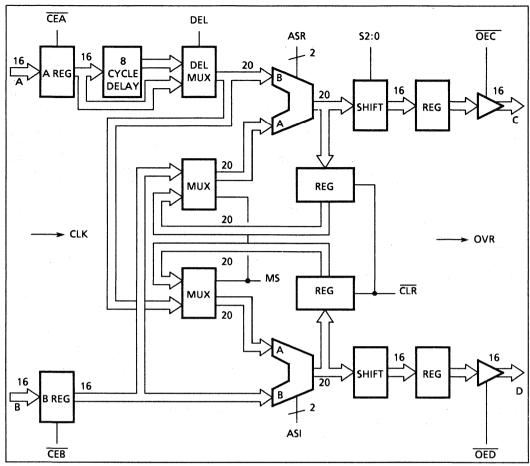

| FIR filtering with the PDSP16112 and PDSP16318              | 169  |

| Interfacing the PDSP family                                 | 171  |

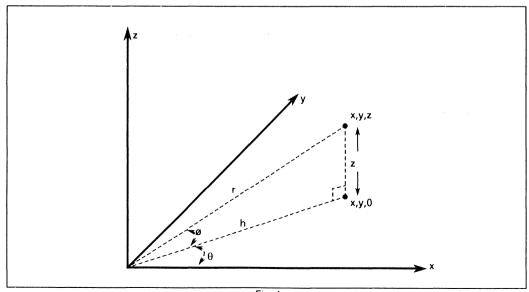

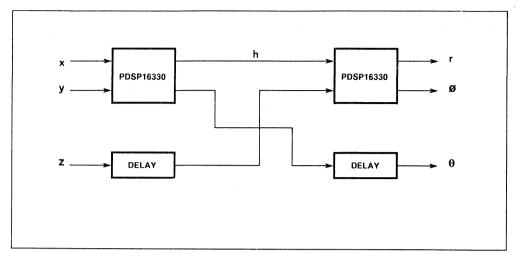

| Three dimensional co-ordinate transforms with the PDSP16330 | 173  |

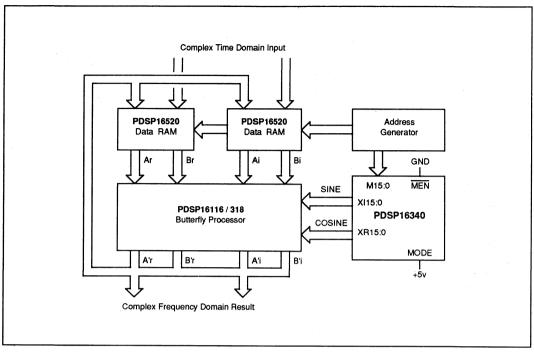

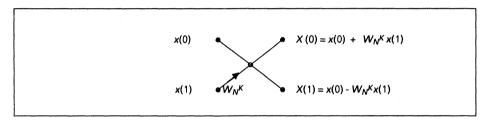

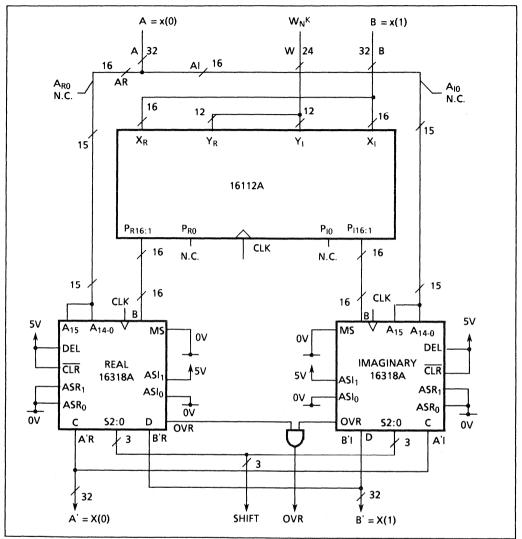

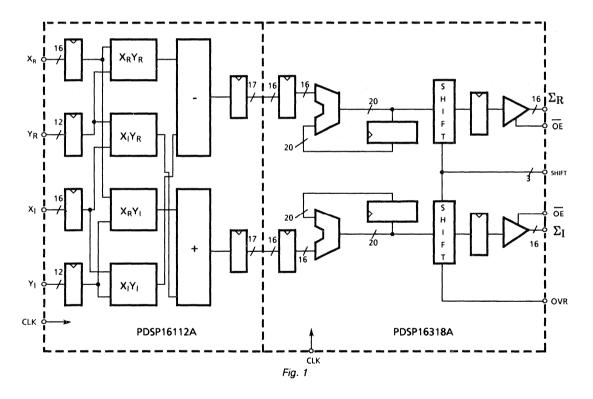

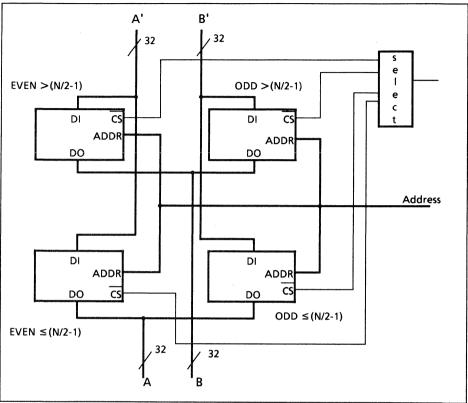

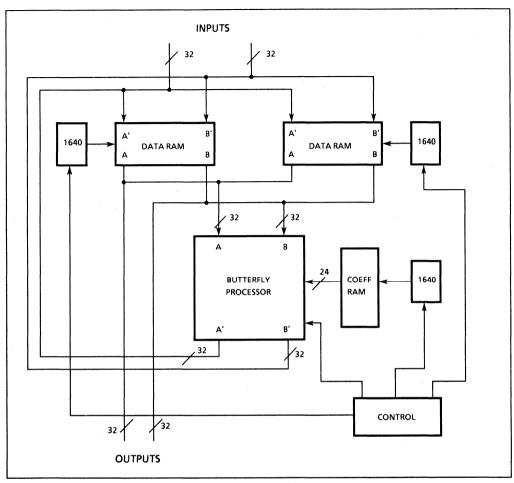

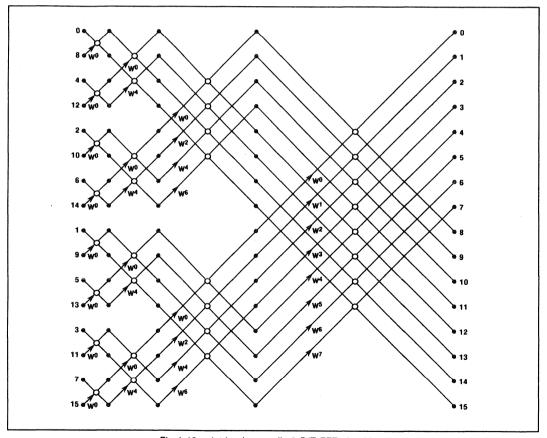

| A radix 2 Butterfly processor                               | 175  |

| Complex signal processing with the PDSP16000 family         | 187  |

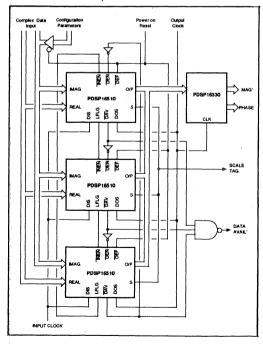

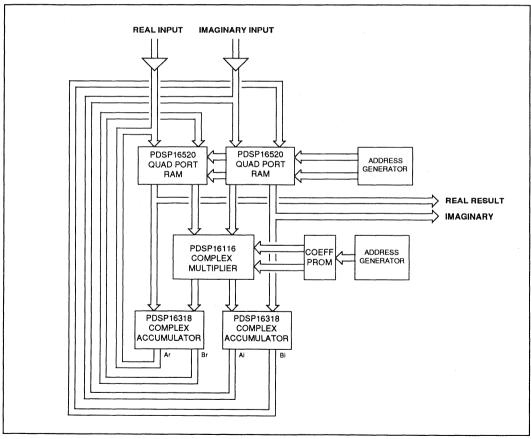

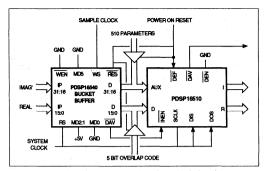

| A fast FFT processor using the PDSP16000 family             | 194  |

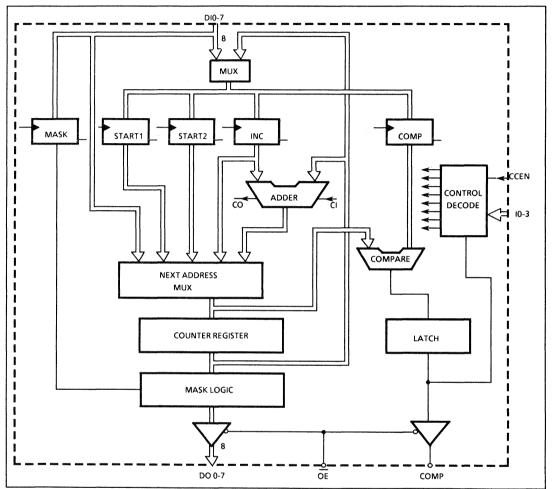

| FFT address generation using the PDSP1640                   | 208  |

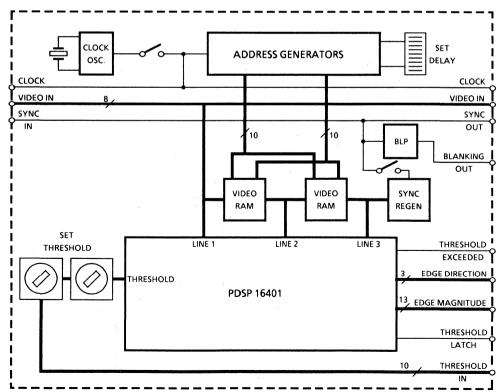

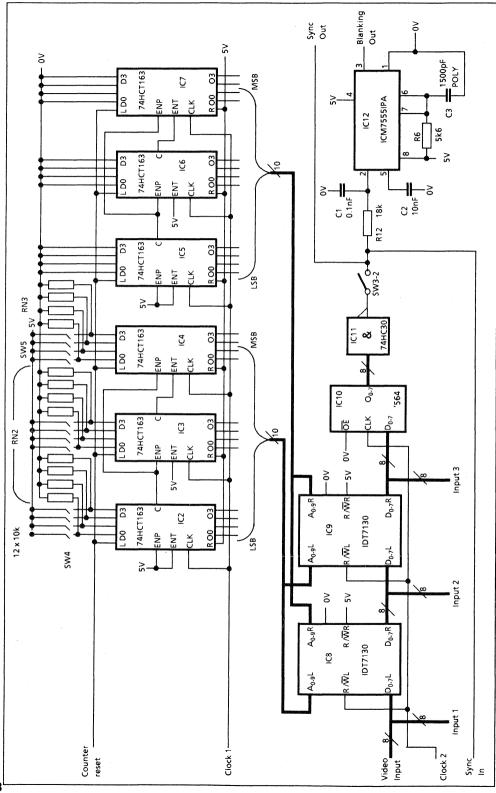

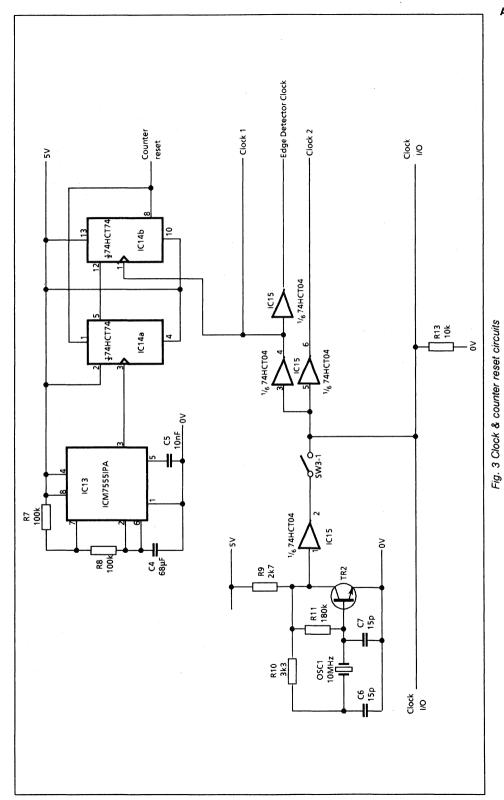

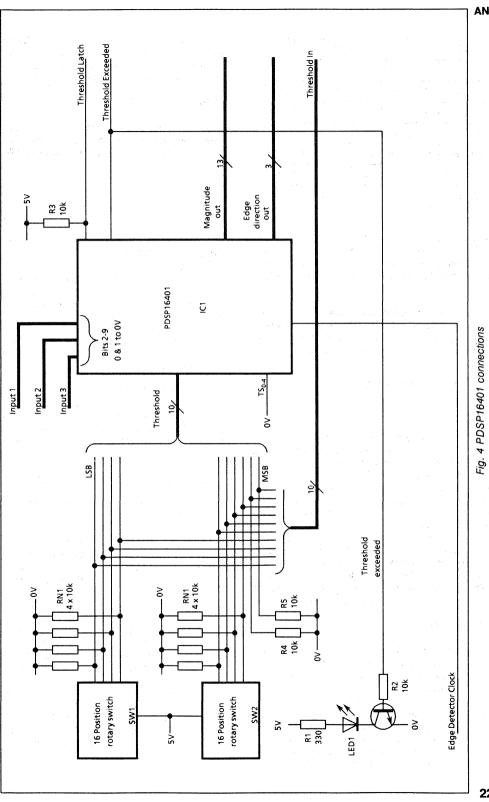

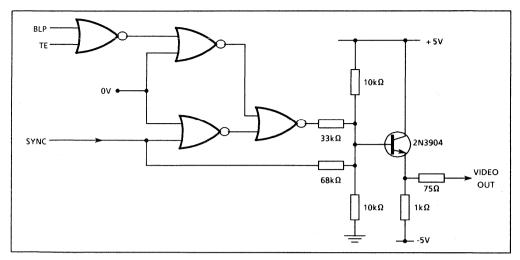

| 2-D edge detector board AP16401                             | 217  |

| Sobel v. PDSP operators                                     | 225  |

| A high resolution FFTprocessor using the PDSP16116          | 226  |

| Optimising the accuracy of an FFT system                    | 249  |

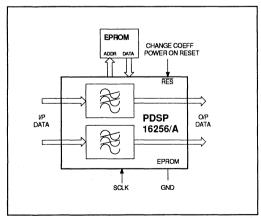

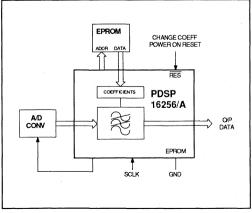

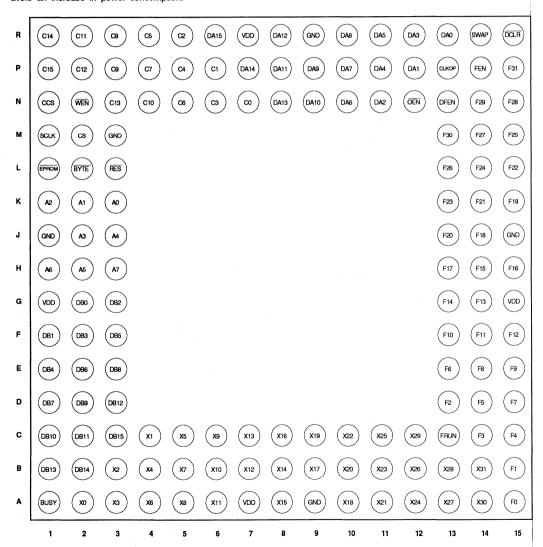

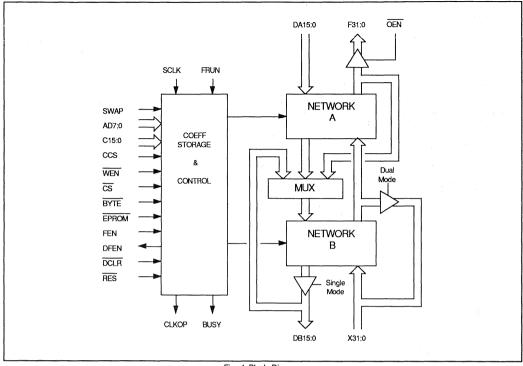

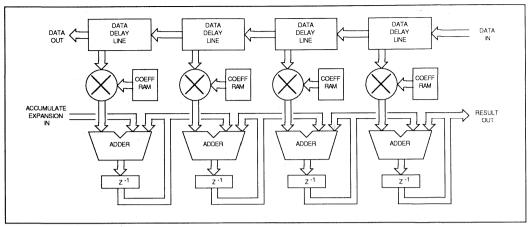

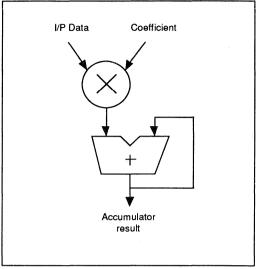

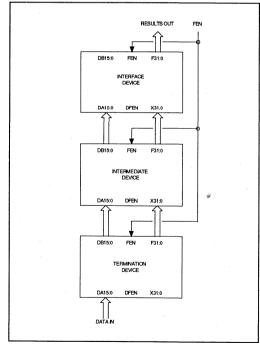

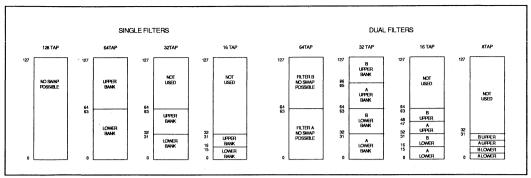

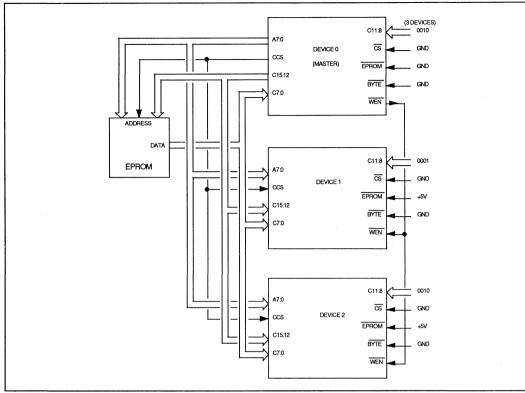

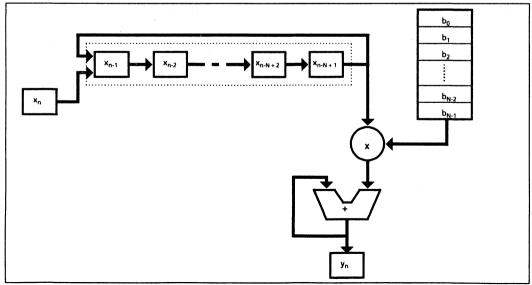

| Digital filtering using the PDSP16256                       | 253  |

| Support tools                                               |      |

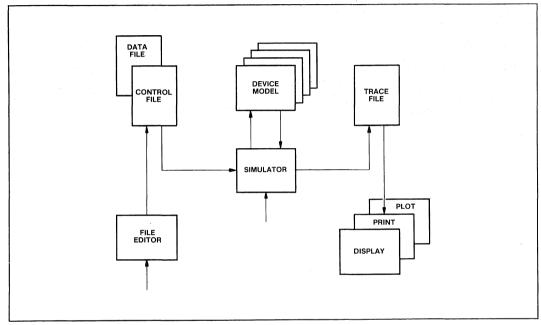

| PDSP demonstrator                                           | 261  |

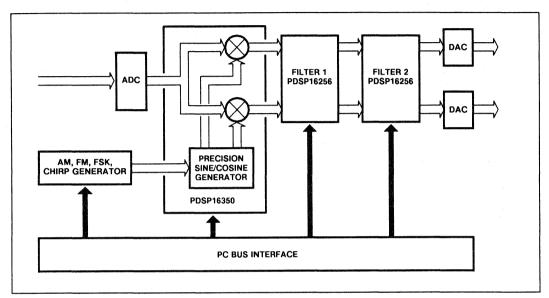

| PDSP16256/PDSP16350 evaluation system                       | 263  |

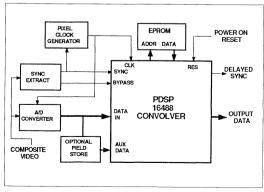

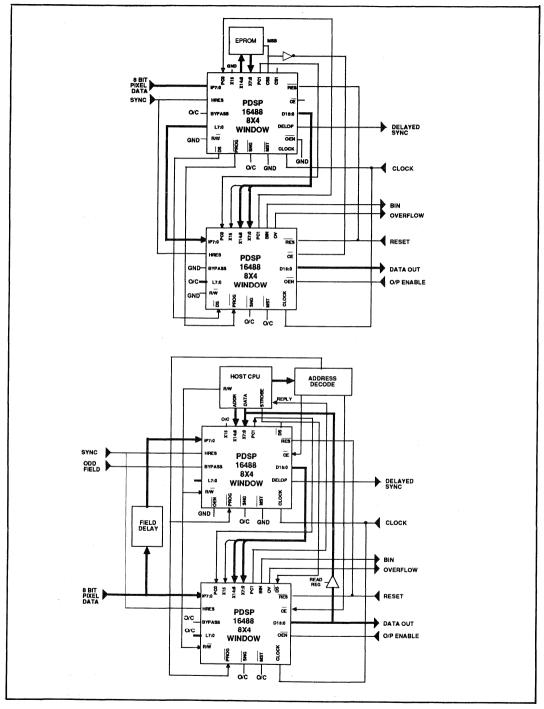

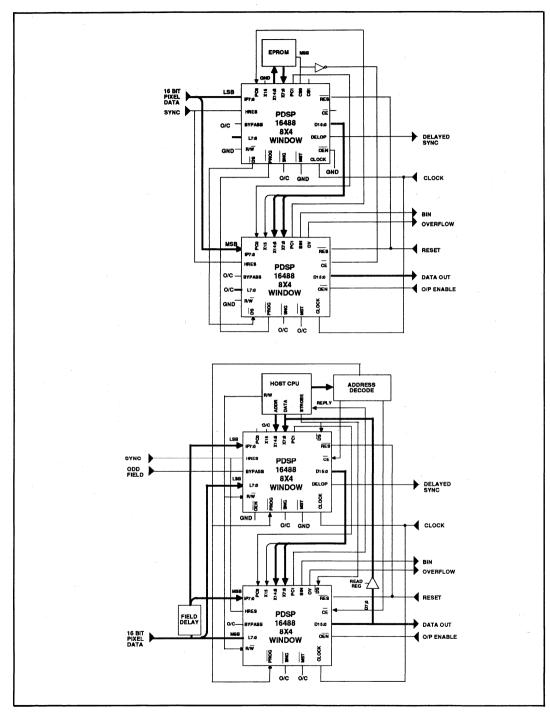

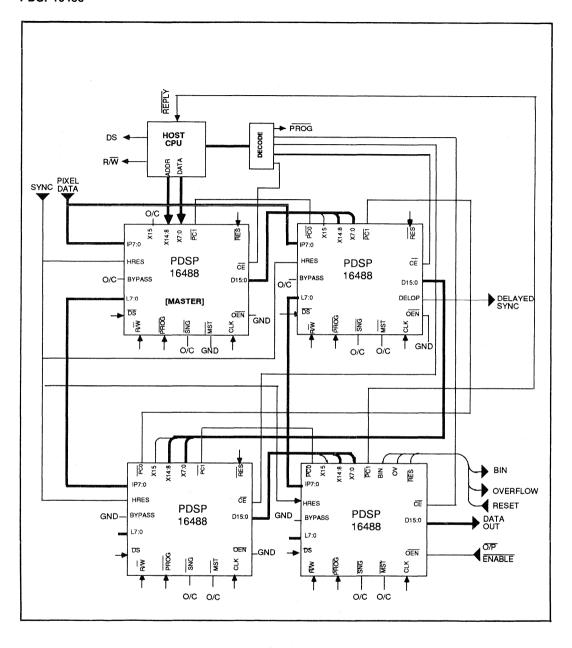

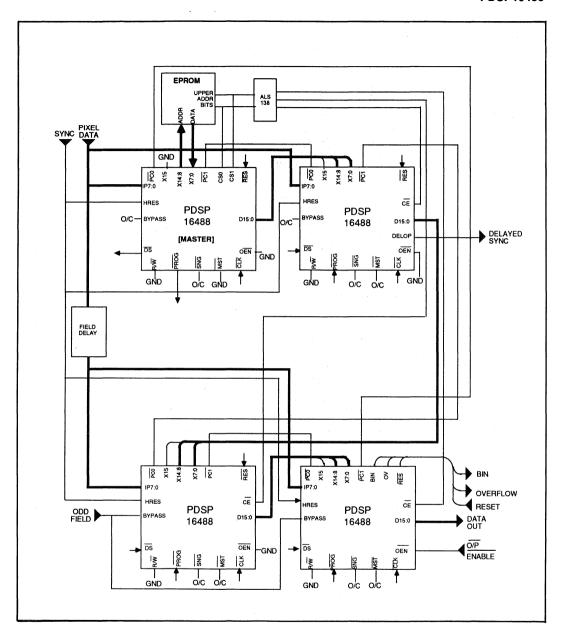

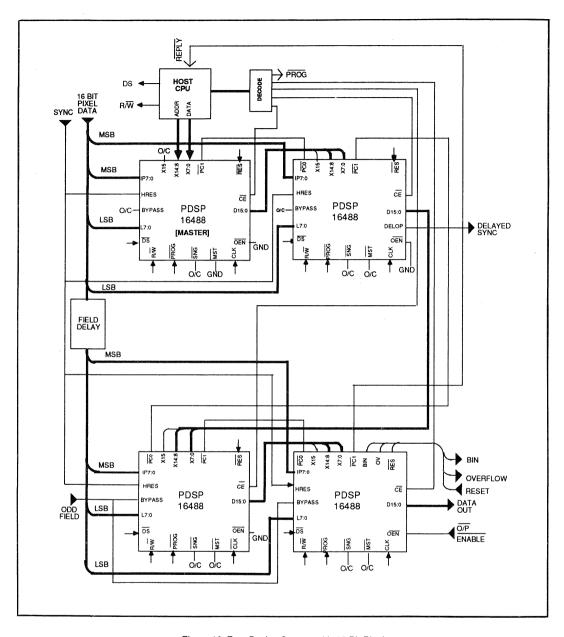

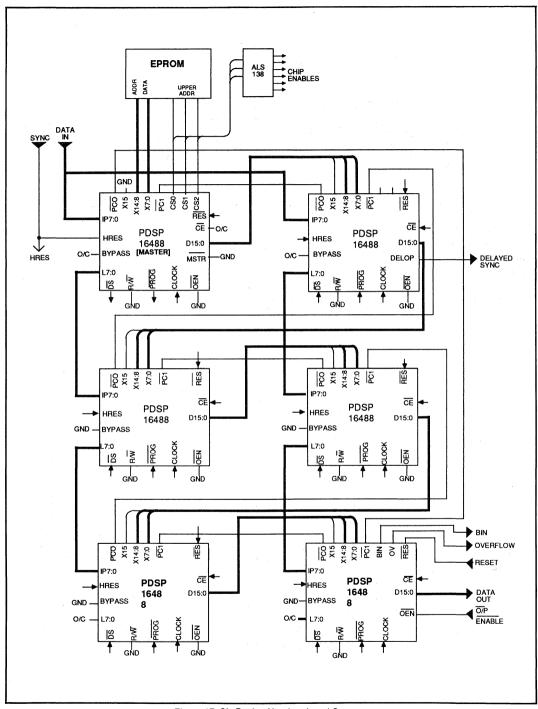

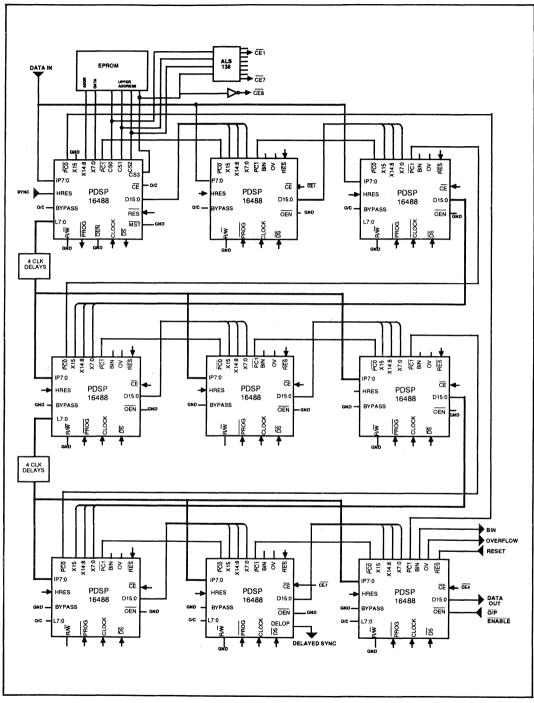

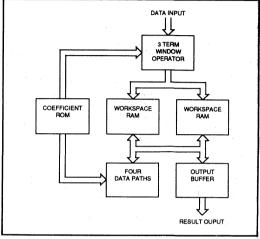

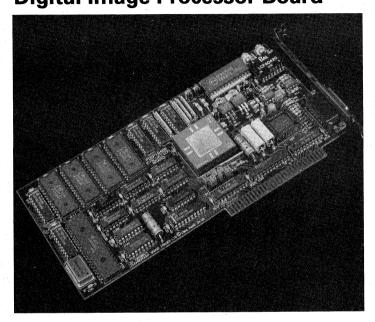

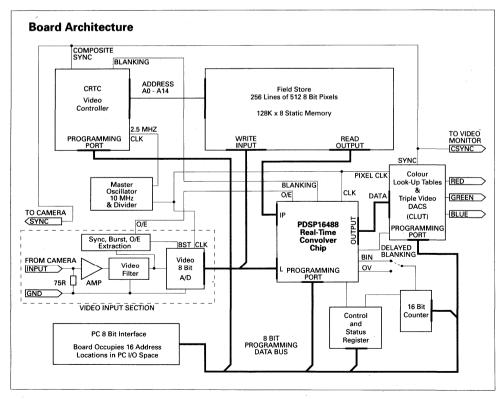

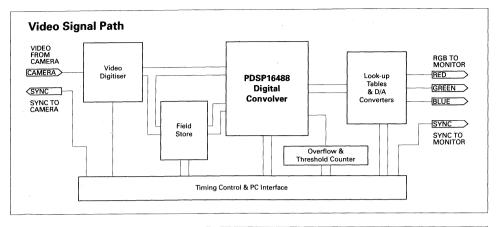

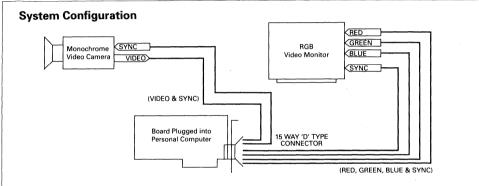

| PDSP16488 real-time digital image processor board           | 265  |

| Data converters for digital signal signal processing        | 269  |

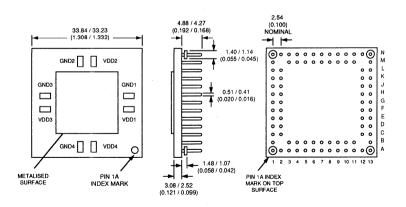

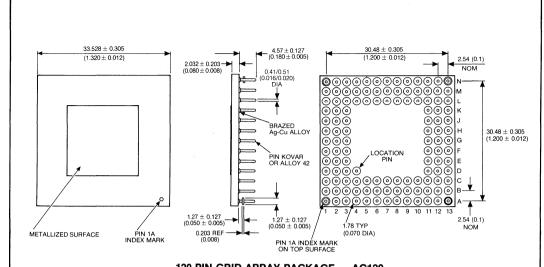

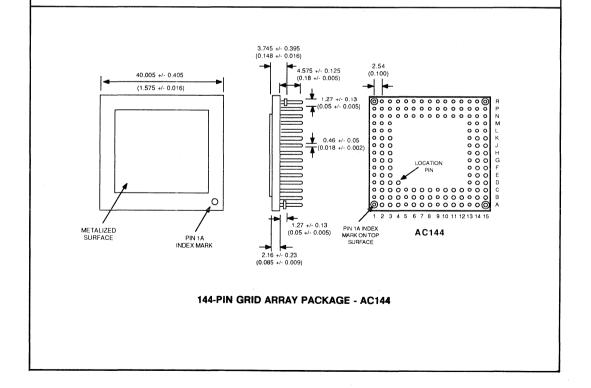

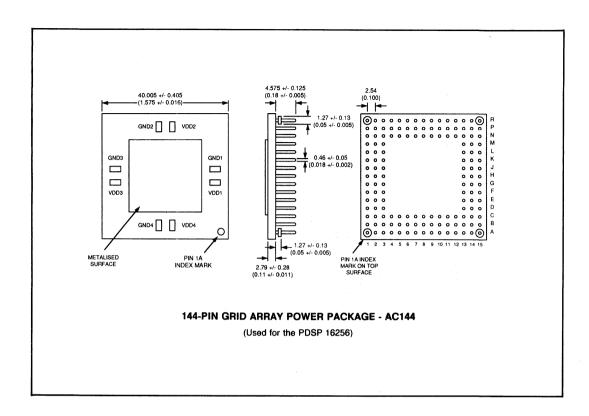

| Package outlines                                            | 271  |

| Locations                                                   | 279  |

# Product index - Building block DSP ICs

# Arithmetic logic units

| Type      | Function               | Speed | Page |

|-----------|------------------------|-------|------|

| PDSP1601A | ALU and barrel shifter | 20MHz | 9    |

### Complex arithmetic

| Туре       | Function                        | Speed | Page |

|------------|---------------------------------|-------|------|

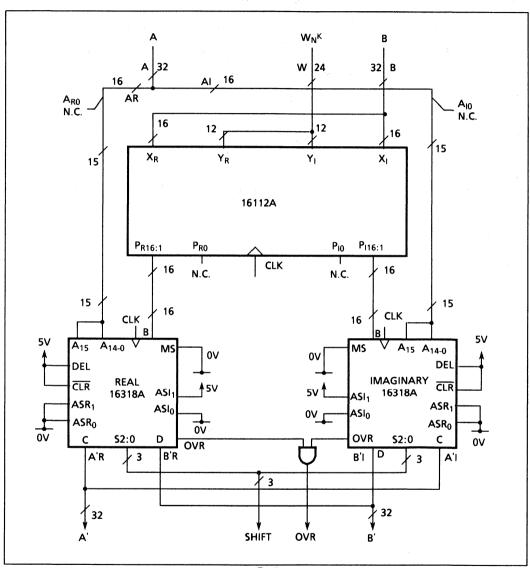

| PDSP16112A | Complex multiplier (16×12 bits) | 20MHz | 31   |

| PDSP16116A | Complex multiplier (16×16 bits) | 20MHz | 37   |

| PDSP16318A | Complex accumulator             | 20MHz | 51   |

# **Support functions**

| Туре      | Function                  | Speed | Page |

|-----------|---------------------------|-------|------|

| PDSP1640  | Address generator         | 20MHz | 23   |

| PDSP16520 | Quad port synchronous RAM | 20MHz | 146  |

# Product index - Algorithm specific DSP ICs

## Image processing

| Туре       | Function                  | Speed | Page |

|------------|---------------------------|-------|------|

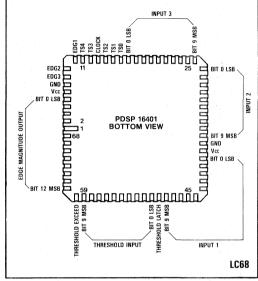

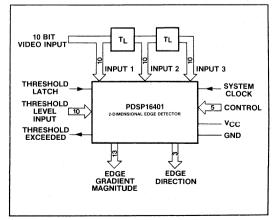

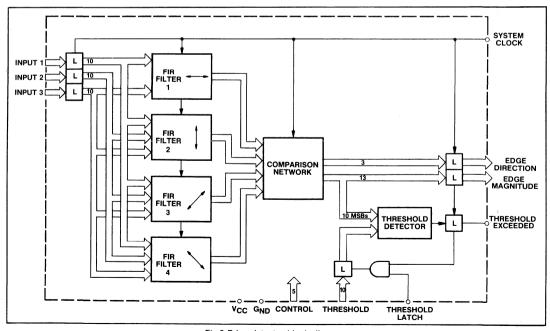

| PDSP16401A | 2-D edge detector         | 22MHz | 95   |

| PDSP16488  | Single-chip 2-D convolver | 40MHz | 100  |

# Digital filtering

| Type       | Function     | n   |        | Speed | Page |

|------------|--------------|-----|--------|-------|------|

| PDSP16256A | Programmable | FIR | filter | 25MHz | 57   |

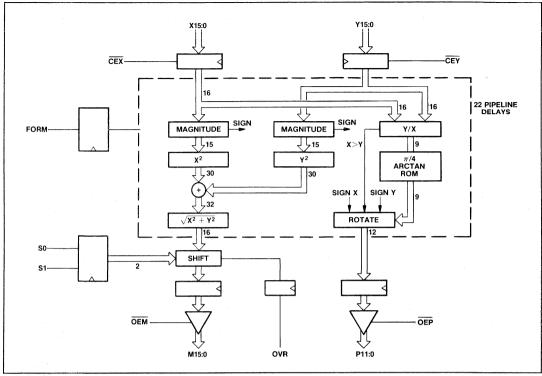

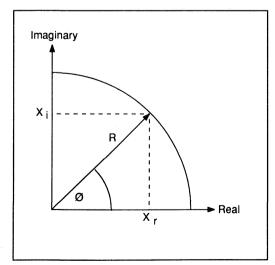

# Co-ordinate conversion

| Туре       | Function                     | Speed | Page |

|------------|------------------------------|-------|------|

| PDSP16330B | Pythagoras processor         | 25MHz | 73   |

| PDSP16340  | Polar to Cartesian converter | 20MHz | 79   |

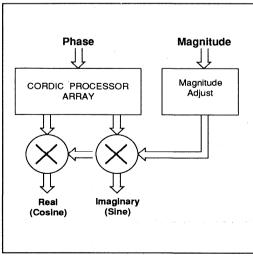

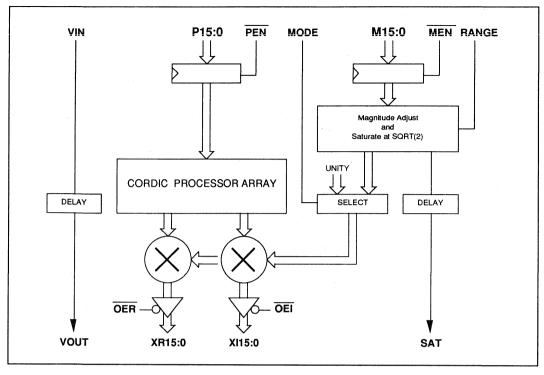

### Waveform generation and modulation

| PDSP16350 | I/Q splitter and NCO | 20MHz | 86   |

|-----------|----------------------|-------|------|

| Туре      | Function             | Speed | Page |

# Frequency domain processing

| Type      | Function                  | Speed | Page |

|-----------|---------------------------|-------|------|

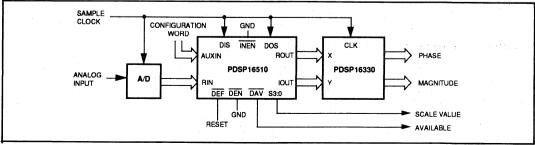

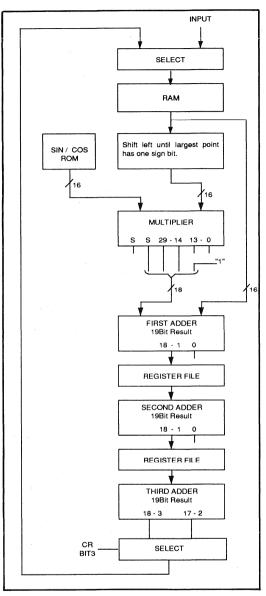

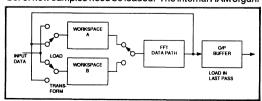

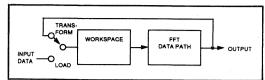

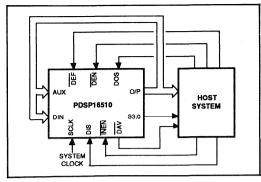

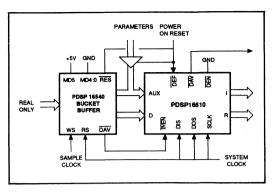

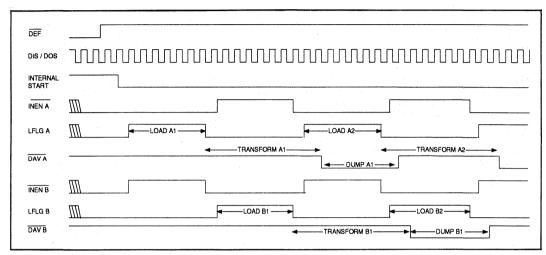

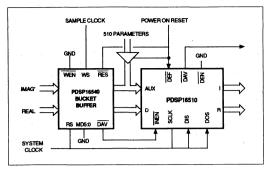

| PDSP16510 | Stand alone FFT processor | 40MHz | 127  |

| PDSP16540 | 32K bucket buffer         | 40MHz | 155  |

# Product list – alpha numeric

| TYPE          | DESCRIPTION                  | PAGE |

|---------------|------------------------------|------|

| PDSP1601/A    | ALU and barrel shifter       | 9    |

| PDSP1640      | Address generator            | 23   |

| PDSP16112/A   | Complex multiplier (16 × 12) | 31   |

| PDSP16116/A   | Complex multiplier (16×16)   | 37   |

| PDSP16256/A   | Programmable FIR filter      | 57   |

| PDSP16318/A   | Complex accumulator          | 51   |

| PDSP16330/A/B | Pythagoras processor         | 73   |

| PDSP16340     | Polar to Cartesian converter | 79   |

| PDSP16350     | I/Q splitter and NCO         | 86   |

| PDSP16401/A   | 2-D edge detector            | 95   |

| PDSP16488     | 2-D convolver                | 100  |

| PDSP16510     | Stand alone FFT processor    | 127  |

| PDSP16520     | Quad port synchronous RAM    | 146  |

| PDSP16540     | 32K bucket buffer            | 155  |

# Technical data

# **PDSP1601/PDSP1601A**

#### **ALU AND BARREL SHIFTER**

The PDSP1601 is a high performance 16-bit arithmetic logic unit with an independent on-chip 16-bit barrel shifter. The PDSP1601A has two operating modes giving 20MHz or 10MHz register-to-register transfer rates.

The PDSP1601 supports Multicycle multiprecision operation. This allows a single device to operate at 20MHz for 16-bit fields, 10MHz for 32-bit fields and 5MHz for 64-bit fields. The PDSP1601 can also be cascaded to produce wider words at the 20MHz rate using the Carry Out and Carry In pins. The Barrel Shifter is also capable of extension, for example the PDSP1601 can be used to select a 16-bit field from a 32-bit input in 100ns.

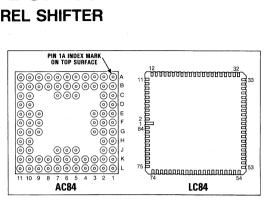

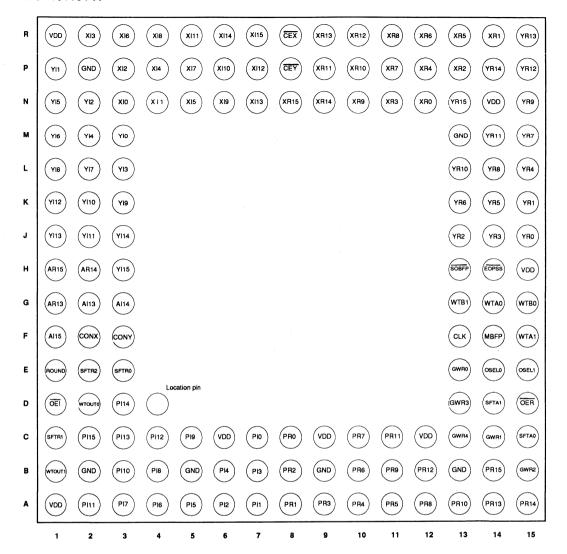

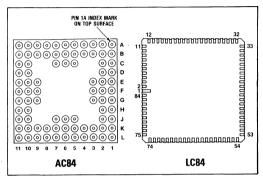

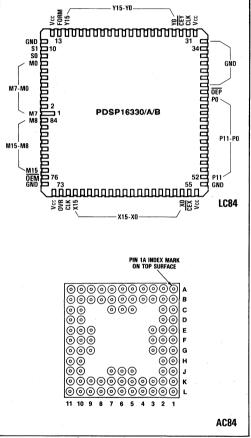

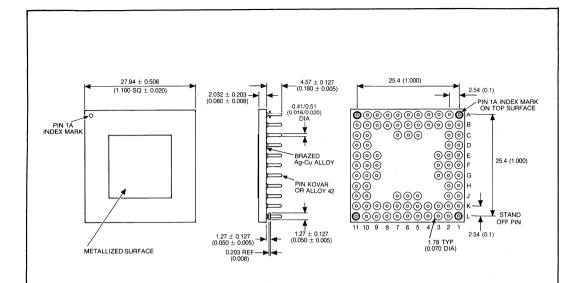

Fig.1 Pin connections - bottom view

#### PIN DESCRIPTIONS

| LC Pin | AC Pin | Function |

|--------|--------|----------|--------|--------|----------|--------|--------|----------|--------|--------|----------|

| 1      | C6     | IA4      | 22     | F3     | GND      | 43     | J6     | IS0      | 64     | F9     | GND      |

| 2      | A6     | MSB      | 23     | G3     | MSA0     | 44     | J7     | IS1      | 65     | F11    | C8       |

| 3      | A5     | MSS      | 24     | G1     | MSA1     | 45     | L7     | IS2      | 66     | E11    | C9       |

| 4      | B5     | B15      | 25     | G2     | A15      | 46     | K7     | IS3      | 67     | E10    | C10      |

| 5      | C5     | B14      | 26     | F1     | A14      | 47     | L6     | SV0      | 68     | E9     | C11      |

| 6      | A4     | B13      | 27     | H1     | A13      | 48     | L8     | SV1      | 69     | D11    | C12      |

| 7      | B4     | B12      | 28     | H2     | A12      | 49     | K8     | SV2      | 70     | D10    | C13      |

| 8      | A3     | B11      | 29     | J1     | A11      | 50     | L9     | SV3      | 71     | C11    | C14      |

| 9      | A2     | B10      | 30     | K1     | A10      | 51     | L10    | SVOE     | . 72   | B11    | C15      |

| 10     | B3     | B9       | 31     | J2     | A9       | 52     | K9     | RS0      | 73     | C10    | OE       |

| 11     | A1     | B8       | 32     | L1     | A8       | 53     | L11    | RS1      | 74     | A11    | BFP      |

| 12     | B2     | B7       | 33     | K2     | A7       | 54     | K10    | VCC      | 75     | B10    | vcc      |

| 13     | C2     | B6       | 34     | КЗ     | A6       | 55     | J10    | RS2      | 76     | B9     | co       |

| 14     | B1     | B5       | 35     | L2     | A5       | 56     | K11    | C0       | 77     | A10    | RA0      |

| 15     | C1     | B4       | 36     | L3     | A4       | 57     | J11    | C1       | 78     | A9     | RA1      |

| 16     | D2     | B3       | 37     | K4     | A3       | 58     | H10    | C2       | 79     | B8     | RA2      |

| 17     | D1     | B2       | 38     | L4     | A2       | 59     | H11    | C3       | 80     | A8     | CI       |

| 18     | E3     | B1       | 39     | J5     | A1       | 60     | F10    | C4       | 81     | B6     | IA0      |

| 19     | E2     | B0       | 40     | K5     | A0       | 61     | G10    | C5       | 82     | B7     | IA1      |

| 20     | E1     | CEB      | 41     | L5     | CEA      | 62     | G11    | C6       | 83     | A7     | IA2      |

| 21     | F2     | CLK      | 42     | K6     | MSC      | 63     | . G9   | C7       | 84     | C7     | IA3      |

#### **FEATURES**

- 16-bit, 32 Instruction 20MHz ALU

- 16-bit, 20MHz Logical, Arithmetic or Barrel Shifter

- Independent ALU and Shifter Operation

- 4 x 16-bit On Chip Scratchpad Registers

- Multiprecision Operation; e.g. 200ns 64-bit Accumulate

- Three Port Structure with Three Internal Feedback Paths Eliminates I/O Bottlenecks

- Block Floating Point Support

- 300mW Maximum Power Dissipation

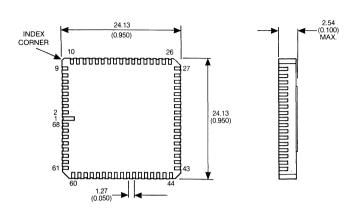

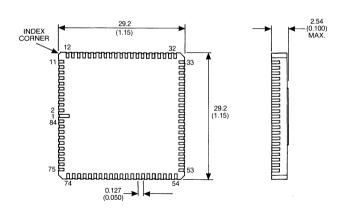

- 84-pin Pin Grid Array or 84 Contact LCC Packages

#### **APPLICATIONS**

- Digital Signal Processing

- Array Processing

- Graphics

- Database Addressing

- High Speed Arithmetic Processors

#### **ASSOCIATED PRODUCTS**

| PDSP16112 | Complex Multiplier         |

|-----------|----------------------------|

| PDSP1640  | 20MHz Address Generator    |

| PDSP16116 | 16 × 16 Complex Multiplier |

| PDSP16318 | Complex Accumulator        |

| PDSP16330 | Pythagoras Processor       |

#### PDSP1601/1601A

#### PIN DESCRIPTIONS

| Symbol           | Pin No.<br>(LC84<br>Package) | Description                                                                                                                                                                                                                                                                                                                       |  |

|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MSB              | 2                            | <b>ALU B-input multiplexer select control</b> .¹ This input is latched internally on the rising edge of CLK.                                                                                                                                                                                                                      |  |

| MSS              | 3                            | Shifter Input multiplexer select control. This input is latched internally on the rising edge of CLK.                                                                                                                                                                                                                             |  |

| B15 - B0         | 4 - 19                       | <b>B Port data input</b> . Data presented to this port is latched into the input register on the rising edge of CLK. B15 is the MSB.                                                                                                                                                                                              |  |

| CEB              | .20                          | Clock enable, B Port input register. When low the clock to this register is enabled.                                                                                                                                                                                                                                              |  |

| CLK              | 21                           | Common clock to all internal registered elements. All registers are loaded, and outputs change on the rising edge of CLK.                                                                                                                                                                                                         |  |

| MSA0 - MSA1      | 23 - 24                      | <b>ALU A-input multiplexer select control</b> . <sup>1</sup> These inputs are latched internally on the rising edge of CLK.                                                                                                                                                                                                       |  |

| A15 - A0         | 25 - 40                      | A Port data input. Data presented to this port is latched into the input register on the rising edge of CLK. A15 is the MSB.                                                                                                                                                                                                      |  |

| CEA              | 41                           | Clock enable, A Port input register. When low the clock to this register is enabled.                                                                                                                                                                                                                                              |  |

| MSC              | 42                           | <b>C-Port multiplexer select control</b> . This input is latched internally on the rising edge of CLK.                                                                                                                                                                                                                            |  |

| ISO - IS3        | 43 - 46                      | Instruction inputs to Barrel Shifter, IS3 $=$ MSB. $^1$ These inputs are latched internally on the rising edge of CLK.                                                                                                                                                                                                            |  |

| SV0 - SV3        | 47 - 50                      | Shift Value I/O Port. This port is used as an input when shift values are supplied from external sources, and as an output when Normalise operations are invoked. The I/O functions are determined by the ISO - IS3 instruction inputs, and by the SVOE control. The shift value is latched internally on the rising edge of CLK. |  |

| SVOE             | 51                           | <b>SV Output enable</b> . When high the SV port can only operate as an input. When low the SV port can act as an input or as an output, according to the ISO - IS3 instruction. This pin should be tied high or low, depending upon the application.                                                                              |  |

| RS0, RS1,<br>RS2 | 52 - 53<br>55                | <b>Instruction inputs to Barrel Shifter registers.</b> <sup>1</sup> These inputs are latched internally on the rising edge of CLK.                                                                                                                                                                                                |  |

| C0 - C15         | 56 - 63<br>65 - 72           | <b>C Port data output</b> . Data output on this port is selected by the C output multiplexer. C15 is the MSB.                                                                                                                                                                                                                     |  |

| ŌĒ               | 73                           | Output enable. The C Port outputs are in a high impedance condition when this control is high.                                                                                                                                                                                                                                    |  |

| BFP              | 74                           | Block Floating Point Flag from ALU, active high.                                                                                                                                                                                                                                                                                  |  |

| СО               | 76                           | Carry out from MSB of ALU.                                                                                                                                                                                                                                                                                                        |  |

| RA0 - RA2        | 77 - 79                      | <b>Instruction inputs to ALU registers.</b> These inputs are latched internally on the rising edge of CLK.                                                                                                                                                                                                                        |  |

| CI               | 80                           | Carry in to LSB of ALU.                                                                                                                                                                                                                                                                                                           |  |

| IAO - IA3<br>IA4 | 81 - 84<br>1                 | <b>Instruction inputs to ALU</b> , $^1$ IA4 = MSB. These inputs are latched internally on the rising edge of CLK.                                                                                                                                                                                                                 |  |

| Vcc              | 54 & 75                      | +5V supply. Both Vcc pins must be connected                                                                                                                                                                                                                                                                                       |  |

| GND              | 22 & 64                      | <b>0V supply</b> . Both GND pins must be connected.                                                                                                                                                                                                                                                                               |  |

NOTES

<sup>1.</sup> All instructions are executed in the cycle commencing with the rising edge of the CLK which latches the inputs.

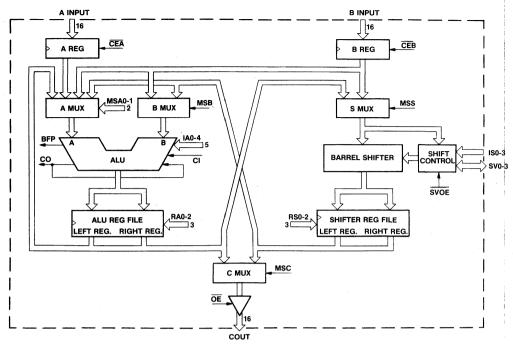

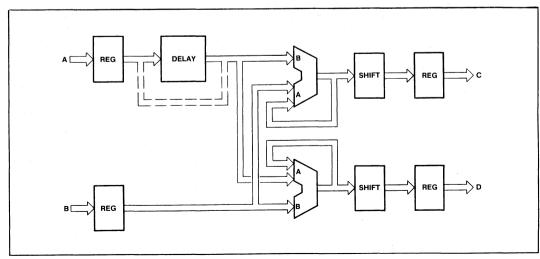

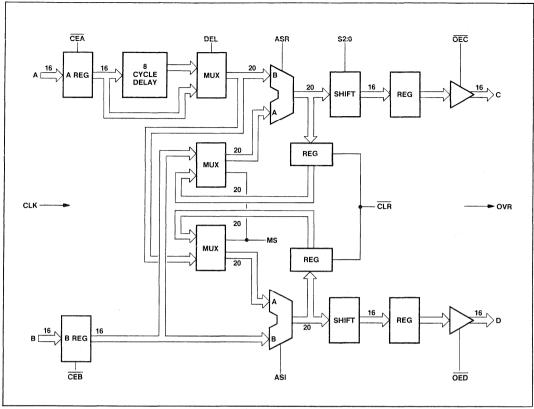

Fig.2 PDSP1601 block diagram.

#### **FUNCTIONAL DESCRIPTION**

The PDSP1601 contains four main blocks: the ALU, the Barrel Shifter and the two Register Files.

#### The ALU

The ALU supports 32 instructions as detailed in Table 1. The inputs to the ALU are selected by the A and B MUXs. Data will fall through from the selected register through the A or B input MUXs and the ALU to the ALU output register file in 50ns for the PDSP1601A (100ns for the PDSP1601).

The ALU instructions are latched, such that the instruction will not start executing until the rising edge of CLK latches the instruction into the device.

The ALU accepts a carry in from the CI input and supplies a carry out to the CO output. Additionally, at the end of each cycle, the carry out from the ALU is loaded into an internal 1 bit register, so that it is available as an input to the ALU on the next cycle. In this manner, multicycle, multiprecision operations are supported. (See MULTICYCLE CASCADE OPERATIONS).

#### **BFP Flag**

The ALU has a user programmable BFP flag. This flag may be programmed to become active at any one of four conditions. Two of these conditions are intended to support Block Floating Point operations, in that they provide flags indicating that the ALU result is within a factor of two or four of overflowing the 16 bit number range. For multiprecision operations the flag is only valid whilst the most significant 16 bit byte is being processed. In this manner the BFP flag may be used over any extended word width.

The remaining two conditions detect either an overflow condition or a zero result. For the overflow condition to be

active the ALU result must have overflowed into the 16th (sign) bit, (this flag is only valid whilst the most significant 16 bit byte is being processed). The zero condition is active if the result from the ALU is equal to zero. For multiprecision operations the zero flag must be active for all of the 16 bit bytes of an extended word.

The BFP flag is programmed by executing one of the four SBFXX instructions (see Table 1). During the execution of any of these four instructions, the output of the ALU is forced to zero.

#### Multicycle/Cascade Operation

The ALU arithmetic instructions contain two or three options for each arithmetic operation.

The ALU is designed to operate with two's complement arithmetic, requiring a one to be added to the LSB for all subtract operations. The instructions set includes instructions that will force a one into the LSB, e.g. MIAX1, AMBX1, BMAX1 (see Table 1).

These instructions are used for the least significant 16 bit byte of any subtract operation.

The user has the option of cascading multiple devices, or multicycling a single device to extend the arithmetic precision. Should the user cascade multiple devices, then the cascade arithmetic instructions using the external CI input should be employed for all but the least significant 16 bit byte, e.g. MIACI, APBCI, BMACI (see Table 1).

Should the user multicycle a single device, then the Multicycle Arithmetic instructions, using the internally registered CO bit should be employed for all but the least significant 16 bit byte, e.g. MIACO, APBCO, AMBCO, BMACO (see Table 1).

Table 1 ALU instructions

#### 1a. ARITHMETIC INSTRUCTIONS

| Inst | IA4-AI0 | Mnemonic | Operation | Operation Function  |            |  |  |

|------|---------|----------|-----------|---------------------|------------|--|--|

| 00   | 00000   | CLRXX    | RESET     | CLEAR ALL REGISTERS |            |  |  |

| 01   | 00001   | MIAX1    | MINUS A   | NA Plus 1           | LSBYTE     |  |  |

| 02   | 00010   | MIACI    | MINUS A   | NA Plus Ci          | CASCADE    |  |  |

| 03   | 00011   | MIACO    | MINUS A   | NA Plus CO          | MULTICYCLE |  |  |

| 04   | 00100   | A2SGN    | A/2       | A/2 Sign Extend     | MSBYTE     |  |  |

| 05   | 00101   | A2RAL    | A/2       | A/2 with RAL LSB    | MULTICYCLE |  |  |

| 06   | 00110   | A2RAR    | A/2       | A/2 with RAR LSB    | MULTICYCLE |  |  |

| 07   | 00111   | A2RSX    | A/2       | A/2 with RSX LSB    | MULTICYCLE |  |  |

| 08   | 01000   | APBCI    | A PLUS B  | A Plus B Plus CI    | CASCADE    |  |  |

| 09   | 01001   | APBCO    | A PLUS B  | A Plus B Plus CO    | MULTICYCLE |  |  |

| 0A   | 01010   | AMBX1    | A MINUS B | A Plus NB Plus 1    | LSBYTE     |  |  |

| 0B   | 01011   | AMBCI    | A MINUS B | A Plus NB Plus CI   | CASCADE    |  |  |

| OC   | 01100   | AMBCO    | A MINUS B | A Plus NB Plus CO   | MULTICYCLE |  |  |

| 0D   | 01101   | BMAX1    | B MINUS A | NA Plus B Plus 1    | LSBYTE     |  |  |

| 0E   | 01110   | BMACI    | B MINUS A | NA Plus B Plus CI   | CASCADE    |  |  |

| 0F   | 01111   | BMACO    | B MINUS A | NA Plus B Plus CO   | MULTICYCLE |  |  |

#### 1b. LOGICAL INSTRUCTIONS

| Inst | IA4-IA0 | Mnemonic | Operation | Function |

|------|---------|----------|-----------|----------|

| 10   | 10000   | ANXAB    | A AND B   | A.B      |

| 11   | 10001   | ANANB    | A AND NB  | A.NB     |

| 12   | 10010   | ANNAB    | NA AND B  | NA.B     |

| 13   | 10011   | ORXAB    | A OR B    | A + B    |

| 14   | 10100   | ORNAB    | NA OR B   | NA + B   |

| 15   | 10101   | XORAB    | A XOR B   | A XOR B  |

| 16   | 10110   | PASXA    | PASS A    | Α        |

| 17   | 10111   | PASNA    | INVERT A  | NA       |

#### 1c. CONTROL INSTRUCTIONS

| Inst | IA4-IA0 | Mnemonic | Operation                                      |

|------|---------|----------|------------------------------------------------|

| 18   | 11000   | SBFOV    | Set BFP Flag to OVR, Force ALU output to zero  |

| 19   | 11001   | SBFU1    | Set BFP Flag to UND 1 Force ALU output to zero |

| 1A   | 11010   | SBFU2    | Set BFP Flag to UND 2 Force ALU output to zero |

| 1B   | 11011   | SBFZE    | Set BFP Flag to ZERO Force ALU output to zero  |

| 1C   | 11100   | OPONE    | Output 0001 Hex                                |

| 1D   | 11101   | OPBYT    | Output 00FF Hex                                |

| 1E   | 11110   | OPNIB    | Output 000F Hex                                |

| 1F   | 11111   | OPALT    | Output 5555 Hex                                |

#### KEY

A = A Input to ALU

B = B Input to ALU

CI = External Carry in to ALU

CO = Internally Registered Carry out from ALU

RAL = ALU Register (Left) RAR = ALU Register (Right)

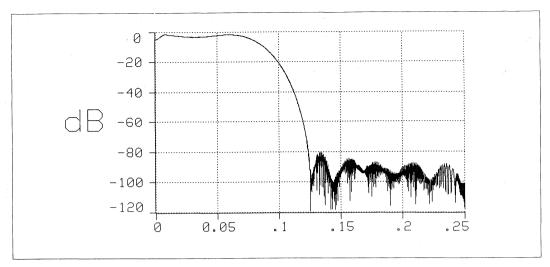

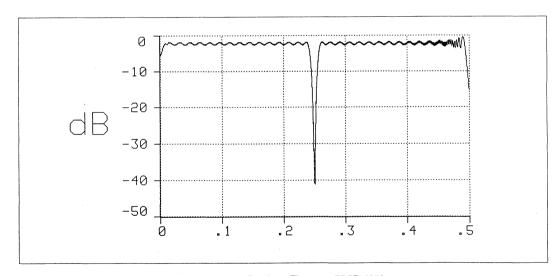

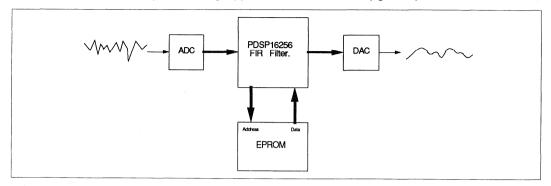

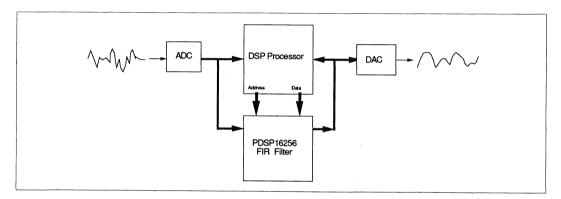

RSX = Shifter Register (Left or Right)

#### **MNEMONICS**

**BMAXX**

CLRXX Clear All Registers to zero

MIAXX Minus A, XX = Carry in to LSB

B Minus A,

ANX-Y AND X = Operand 1, Y = Operand 2

ORX-Y OR X = Operand 1, Y = Operand 2

XORXY Exclusive OR X = Operand 1, Y = Operand 2

XX = Carry in to LSB

PASXX Pass XX = Operand SBFXX Set BFP Flag XX = Function OPXXX Output Constant XXX = Value

#### Divide by Two

The ALU has four (A2SGN, A2RAL, A2RAR, A2RSX) instructions used for right shifting (dividing by two) extended precision words. These words, (up to 64 bits) may be stored in the two on-chip register files. When the least significant 16 bit word is shifted, the vacant MSB must be filled with the LSB from the next most significant 16 bit byte. This is achieved via the A2RAL, A2RAR or A2RSX instructions which indicate the source of the new MSB (see ALU INSTRUCTION SET).

When the most significant 16 bit byte is right shifted, the MSB must be filled with a duplicate of the original MSB so as to maintain the correct sign (Sign Extension). This operation is achieved via the A2SGN instruction (see Table 1).

#### Constants

The ALU has four instructions (OPONE, OPBYT, OPNIB. OPALT) that force a constant value onto the ALU output. These values are primarily intended to be used as masks, or the seeds for mask generation, for example, the OPONE instruction will set a single bit in the least significant position. This bit may be rotated any where in the 16 bit field by the Barrel Shifter, allowing the AND function of the ALU to perform bit-pick operations on input data.

#### **CLR**

The ALU instruction CLRXX is used as a Master Reset for the entire device. This instruction has the effect of:

- 1. Clearing ALU and Barrel Shifter register files to zero.

- Clearing A and B port input registers to zero.

- Clearing the R1 and R2 shift control registers to zero.

- Clearing the internally registered CO bit to zero.

- Programming the BFP flag to detect overflow conditions.

#### The Barrel Shifter

The Barrel Shifter supports 16 instructions as detailed in Table 2. The input to the Barrel Shifter is selected by the S MUX. Data will fall through from the selected register. through the S MUX and the Barrel Shifter to the shifter output register file in 50ns for the PDSP1601A (100ns for the PDSP1601).

The Barrel Shifter instructions are latched, such that the instructions will not start executing until the rising edge of CLK latches the instruction into the device.

The Barrel Shifter is capable of Logical Arithmetic or Barrel Shifts in either direction.

- Logical shifts discard bits that exit the 16 bit field and fill spaces with zeros.

- Arithmetic shifts discard bits that exit the 16 bit field and fill spaces with duplicates of the original MSB.

- C. Barrel Shifts rotate the 16 bit fields such that bits that exit the 16 bit field to the left or right reappear in the vacant spaces on the right or left.

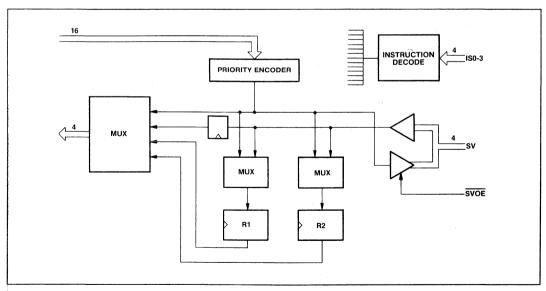

The amount of shift applied is encoded onto the 4 bit Barrel Shifter input as illustrated in Table 3. The type of shift and the amount are determined by the shift control block. The shift control block (see Fig.3) accepts and decodes the four bit ISO-3 instruction. The shift control block contains a priority encoder and two, user programmable 4 bit registers R1 and

There are four possible sources of shift value that can be passed onto the Barrel Shifter, these are:

- The Priority Encoder

- The SV input

- The R1 register

- The R2 register

| Inst | IS3-IS0 | Mnemonic | Function                     | I/O |

|------|---------|----------|------------------------------|-----|

| 0    | 0000    | LSRSV    | Logical Shift Right by SV    | ı   |

| 1:   | 0001    | LSLSV    | Logical Shift Left by SV     | 1   |

| 2    | 0010    | BSRSV    | Barrel Shift Right by SV     | 1   |

| . 3  | 0011    | BSLSV    | Barrel Shift Left by SV      | 1   |

| 4    | 0100    | LSRR1    | Logical Shift Right by R1    | X   |

| 5    | 0101    | LSLR1    | Logical Shift Left by R1     | X   |

| 6    | 0110    | LSRR2    | Logical Shift Right by R2    | Х   |

| 7    | 0111    | LSLR2    | Logical Shift Left by R2     | Х   |

| 8    | 1000    | LR1SV    | Load Register 1 From SV      | 1   |

| 9    | 1001    | LR2SV    | Load Register 2 From SV      | 1   |

| Α .  | 1010    | ASRSV    | Arithmetic Shift Right by SV | 1   |

| В    | 1011    | ASRR1    | Arithmetic Shift Right by R1 | Х   |

| С    | 1100    | ASRR2    | Arithmetic Shift Right by R2 | Х   |

| D    | 1101    | NRMXX    | Normalise Output PE          | 0   |

| Е    | 1110    | NRMR1    | Normalise Output PE, Load R1 | 0   |

| F    | 1111    | NRMR2    | Normalise Output PE, Load R2 | 0   |

Table 2 Barrel shifter instructions

| KEY |                                | MNEMO | NICS              |       |                                        |

|-----|--------------------------------|-------|-------------------|-------|----------------------------------------|

| SV  | = Shift Value                  | LSXYY | Logical Shift,    | Χ     | = Direction YY = Source of Shift Value |

| R1  | = Register 1                   | BSXYY | Barrel Shift,     | Χ     | = Direction YY = Source of Shift Value |

| R2  | = Register 2                   | ASXYY | Arithmetic Shift, | X     | = Direction YY = Source of Shift Value |

| PE  | = Priority Encoder Output      | LXXYY | Load              | XX    | = Target YY = Source                   |

| 1   | ⇒ SV Port operates as an Input | NRMYY | Normalise by PE   | , Out | out PE value on SV Port, Load YY Reg   |

=> SV Port operates as an Output Х => SV Port in a High Impedance State

0

#### PDSP1601/1601A

| SV3 | SV2 | SV1 | SV0 | Shift     |

|-----|-----|-----|-----|-----------|

| 0   | 0   | 0   | 0   | No shift  |

| 0   | 0   | 0   | 1   | 1 place   |

| 0   | 0   | 1   | 0   | 2 places  |

| 0   | 0   | 1   | 1   | 3 places  |

| 0   | 1 1 | 0   | 0   | 4 places  |

| 0   | 1 1 | 0   | 1   | 5 places  |

| 0   | 1   | 1   | 0   | 6 places  |

| 0   | 1   | 1   | 1   | 7 places  |

| 1   | 0   | 0   | 0   | 8 places  |

| 1   | 0   | 0   | 1   | 9 places  |

| 1   | 0   | 1   | 0   | 10 places |

| 1   | 0   | 1   | 1   | 11 places |

| 1   | 1   | 0   | 0   | 12 places |

| 1   | 1   | 0   | 1   | 13 places |

| 1   | 1   | 1   | 0   | 14 places |

| 1   | 1   | 1   | 1   | 15 places |

Table 3 Barrel shifter codes

#### **Priority Encoder**

If the priority encoder is selected as the source of the shift value (instructions:- NRMXX, NRMR1, MRMRZ), then within one 100ns cycle or two 50ns cycles for the PDSP1601A (one 200ns or two 100ns cycles for the PDSP1601), the shift circuitry will:

- (1) Priority encode the 16 bit input to the Barrel Shifter and place the 4 bit value in either of the R1 or R2 registers and output the value on the SV port (if enabled by SVOE).

- (2) Shift the 16 bit input by the amount indicated by the Priority Encoder such that the output from the Barrel Shifter is a normalised value.

#### **SV** Input

If the SV port is selected as the source of the shift value, then the input to the Barrel Shifter is shifted by the value stored in the internal SV register.

#### SVOE

The SV port acts as an input or an output depending upon the ISO-3 instruction. If the user does not wish to use the normalise instructions, then the SV port may be forced to be input only by tying the  $\overline{\text{SVOE}}$  control high. In this mode the SV port may be considered an extension of the instruction inputs.

#### R1 and R2 Registers

The R1 and R2 registers may be loaded from the Priority Encoder (NRMR1 and NRMR2) or from the SV input (LR1SV, LR2SV).

Whilst the latter two instructions are executing, the Barrel Shifter will pass its input to the output unshifted.

Fig.3 Shift control block

#### The Register Files

There are two on-chip register files (ALU and Shifter), each containing two 16 bit registers and each supporting 8 instructions (see Table 4). The instructions for the ALU register file and the Barrel Shifter Register file are the same.

The Inputs to the register files come from either the ALU or the Barrel Shifter, and are loaded into the Register files on the rising edge of CLK.

The register file instructions are latched such that the instruction will not start executing until the rising edge of the

CLK latches the instruction into the device.

The register file instructions (see Table 4) allow input data to be loaded into either, neither or both of the registers. Data is loaded at the end of the cycle in which the instruction is executing.

The register file instructions allow the output to be sourced from either of the two registers, the selected output will be valid during the cycle in which the instruction is executing.

|      | ALU REGISTER INSTRUCTIONS    |           |                                               |  |  |  |

|------|------------------------------|-----------|-----------------------------------------------|--|--|--|

| Inst | t RA2-RA0 Mnemonic Operation |           |                                               |  |  |  |

| 0    | 000                          | LLRRR     | Load Left Reg Output Right Reg                |  |  |  |

| 1    | 001                          | LRRLR     | Load Right Reg Output Left Reg                |  |  |  |

| 2    | 010                          | LLRLR     | Load Left Register, Output Left Reg           |  |  |  |

| 3    | 011                          | LRRRR     | Load Right Register, Output Right Reg         |  |  |  |

| 4    | 100                          | LBRLR     | Load Both Registers, Output Left Reg          |  |  |  |

| 5    | 101                          | NOPRR     | No Load Operation, Output Right Reg           |  |  |  |

| 6    | 110                          | NOPLR     | No Load Operation, Output Left Reg            |  |  |  |

| 7    | 111                          | NOPPS     | No Load Operation, Pass ALU Result            |  |  |  |

|      |                              | SHIFTER R | EGISTER INSTRUCTIONS                          |  |  |  |

| Inst | RS2-RS0                      | Mnemonic  | Operation                                     |  |  |  |

| 0    | 000                          | LLRRR     | Load Left Reg Output Right Reg                |  |  |  |

| 1    | 001                          | LRRLR     | Load Right Reg Output Left Reg                |  |  |  |

| 2    | 010                          | LLRLR     | Load Left Register, Output Left Reg           |  |  |  |

| 3    | 011                          | LRRRR     | Load Right Register, Output Right Reg         |  |  |  |

| 4    | 100                          | LBRLR     | Load Both Registers, Output Left Reg          |  |  |  |

| 5    | 101                          | NOPRR     | No Load Operation, Output Right Reg           |  |  |  |

| 6    | 110                          | NOPLR     | No Load Operation, Output Left Reg            |  |  |  |

|      |                              |           |                                               |  |  |  |

| 7    | 111                          | NOPPS     | No Load Operation, Pass Barrel Shifter Result |  |  |  |

Table 4 ALU and shift register instructions mnemonics

#### **MNEMONICS**

| LXXYY | Load XX = Target,    | YY | = Source of Output |

|-------|----------------------|----|--------------------|

| LBOXX | Load Both Registers, | XX | = Source of Output |

| NOPXX | No Load Operation,   | XX | = Source of Output |

#### PDSP1601/1601A

#### Multiplexers

There are four user selectable on-chip multiplexers (A-MUX, B-MUX, S-MUX and C-MUX).

These four multiplexers support instructions as tabulated in Table 5.

The MUX instructions are latched such that the instruction will not start executing until the rising edge of CLK latches the instruction onto the device.

|       |                                  | MSA1   | MSA              | Output                                                   |  |

|-------|----------------------------------|--------|------------------|----------------------------------------------------------|--|

| A-MUX | MARAX<br>MAAPR<br>MABPR<br>MARSX | 0      | 0<br>1<br>0<br>1 | 1 A-PORT INPUT                                           |  |

|       | MSB Output                       |        | Output           |                                                          |  |

| B-MUX |                                  | 0      |                  | B-PORT INPUT<br>SHIFTER REGISTER FILE OUTPUT             |  |

| MSS   |                                  | Output |                  |                                                          |  |

| S-MUX |                                  | 0      |                  | B-PORT INPUT<br>ALU REGISTER FILE OUTPUT                 |  |

| C-MUX |                                  | MSC    |                  | Output                                                   |  |

|       |                                  | 0<br>1 |                  | ALU REGISTER FILE OUTPUT<br>SHIFTER REGISTER FILE OUTPUT |  |

Table 5

#### **INSTRUCTION SET**

#### **ALU Arithmetic Instructions**

| Mnemonic | Op Code | Function                                                                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLRXX    | <00>    | On the rising edge of CLK at the end of the cycle in which this instruction is executing, the A Port, B Port, ALU, Barrel Shifter, and Shift Control Registers will be loaded with zeros. The internal registered CO will also be set to zero, and the BFP flag will be set to activate on overflow conditions. |

| MIAX1    | <01>    | The A input to the ALU is inverted and a one is added to the LSB.                                                                                                                                                                                                                                               |

| MIACI    | <02>    | The A input to the ALU is inverted and the CI input is added to the LSB.                                                                                                                                                                                                                                        |

| MIACO    | <03>    | The A input to the ALU is inverted and the CO output from the ALU on the previous cycle is added to the LSB.                                                                                                                                                                                                    |

| A2SGN    | <04>    | The A input to the ALU is right shifted one bit position. The LSB is discarded, and the vacant MSB is filled by duplicating the original MSB (Sign Extension).                                                                                                                                                  |

| A2RAL    | <05>    | The A input to the ALU is right shifted one bit position. The LSB is discarded, and the vacant MSB is filled with the LSB from the ALU left register.                                                                                                                                                           |

| A2RAR    | <06>    | The A input to the ALU is right shifted one bit position. The LSB is discarded, and the vacant MSB is filled with the LSB from the ALU right register.                                                                                                                                                          |

| A2RSX    | <07>    | The A input to the ALU is right shifted one bit position. The LSB is discarded, and the vacant MSB is filled with the LSB from the B input to the ALU.                                                                                                                                                          |

| APBCI    | <08>    | The A input to the ALU is added to the B input, and the CI input is added to the LSB.                                                                                                                                                                                                                           |

| APBCO    | <09>    | The A input to the ALU is added to the B input, and the CO out from the ALU on the previous cycle is added to the LSB.                                                                                                                                                                                          |

| AMBX1    | <0A>    | The A input to the ALU is added to the inverted B input, and a one is added to the LSB.                                                                                                                                                                                                                         |

| AMBCI    | <0B>    | The A input to the ALU is added to the inverted B input, and the CI input is added to the LSB.                                                                                                                                                                                                                  |

| AMBCO    | <0C>    | The A input to the ALU is added to the inverted B input, and the CO out from the ALU on the previous cycle is added to the LSB.                                                                                                                                                                                 |

| BMÄX1    | <0D>    | The inverted A input to the ALU is added to the B input, and a one is added to the LSB.                                                                                                                                                                                                                         |

| BMACI    | <0E>    | The inverted A input to the ALU is added to the B input, and the CI input is added to the LSB.                                                                                                                                                                                                                  |

| ВМАСО    | <0F>    | The inverted A input to the ALU is added to the B input, and the CO out from the ALU on the previous cycle is added to the LSB.                                                                                                                                                                                 |

#### **ALU Logical Instructions**

| Mnemonic | Op Code | Function                                                                     |

|----------|---------|------------------------------------------------------------------------------|

| ANXAB    | <10>    | The A input to the ALU is logically 'ANDed' with the B input.                |

| ANANB    | <11>    | The A input to the ALU is logically 'ANDed' with the inverse of the B input. |

| ANNAB    | <12>    | The inverse of the A input to the ALU is logically 'ANDed' with the B input. |

| ORXAB    | <13>    | The A input to the ALU is logically 'ORed' with the B input.                 |

| ORNAB    | <14>    | The inverse of the A input to the ALU is logically 'ORed' with the B input.  |

| XORAB    | <15>    | The A input to the ALU is logically Exclusive-ORed with the B input.         |

| PASXA    | <16>    | The A input to the ALU is passed to the output.                              |

| PASNA    | <17>    | The inverse of the A input to the ALU is passed to the output.               |

#### PDSP1601/1601A

#### **ALU Control Instructions**

| Mnemonic | Op Code | Function                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBFOV    | <18>    | The BFP flag is programmed to activate when an ALU operation causes an overflow of the 16 bit number range. This flag is logically the exclusive-or of the carry into and out of the MSB of the ALU. For the most significant Byte this flag indicates that the result of an arithmetic two's complement operation has overflowed into the sign bit. The output of the ALU is forced to zero for the duration of this instruction. |

| SBFU1    | <19>    | The BFP flag is programmed to activate when an ALU operation comes within a factor of two of causing an overflow of the 16 bit number range. For the most significant Byte this flag indicates that the result of an arithmetic two's complement operation is within a factor of two of overflowing into the sign bit. The output of the ALU is forced to zero for the duration of this instruction.                               |

| SBFU2    | <1A>    | The BFP flag is programmed to activate when an ALU operation comes within a factor of four of causing an overflow of the 16 bit number range. For the most significant Byte this flag indicates that the result of an arithmetic two's complement operation is within a factor of four of overflowing into the sign bit. The output of the ALU is forced to zero for the duration of this instruction.                             |

| SBFZE    | <1B>    | The BFP flag is programmed to activate when an ALU operation causes a result of zero. The output of the ALU is forced to zero for the duration of this instruction. During the execution of this instruction the BFP flag will become active.                                                                                                                                                                                      |

| OPONE    | <1C>    | The ALU will output the binary value 0000000000001, the MSB on the left.                                                                                                                                                                                                                                                                                                                                                           |

| OPBYT    | <1D>    | The ALU will output the binary value 00000000111111111, the MSB on the left.                                                                                                                                                                                                                                                                                                                                                       |

| OPNIB    | <1E>    | The ALU will output the binary value 00000000001111, the MSB on the left.                                                                                                                                                                                                                                                                                                                                                          |

| OPALT    | <1F>    | The ALU will output the binary value 0101010101010101, the MSB on the left.                                                                                                                                                                                                                                                                                                                                                        |

#### **Barrel Shifter Instructions**

| Mnemonic | Op Code | Function                                                                                                                                                                                                                                                        |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSRSV    | <0>     | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number present in the SV register. The LSBs are discarded, and the vacant MSBs are filled with zeros.                                |

| LSLSV    | <1>     | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number present in the SV register. The MSBs are discarded, and the vacant LSBs are filled with zeros.                                 |

| BSRSV    | <2>     | The 16 bit input to the Barrel Shifter is rotated to the right by the number of places indicated by the magnitude of the four bit number present in the SV register. The LSBs that exit the 16 bit field to the right, reappear in the vacant MSBs on the left. |

| BSLSV    | <3>     | The 16 bit input to the Barrel Shifter is rotated to the left by the number of places indicated by the magnitude of the four bit number present in the SV register. The MSBs that exit the 16 bit field to the left, reappear in the vacant LSBs on the right.  |

| LSRR1    | <4>     | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number resident within the R1 register. The LSBs are discarded, and the vacant MSBs are filled with zeros.                           |

| LSLR1    | <5>     | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number resident within the R1 register. The MSBs are discarded, and the vacant LSBs are filled with zeros.                            |

| LSRR2    | <6>     | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number resident within the R2 register. The LSBs are discarded, and the vacant MSBs are filled with zeros.                           |

| LSLR2    | <7>     | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number resident within the R2 register. The MSBs are discarded, and the vacant LSBs are filled with zeros.                            |

| Mnemonic | Op Code | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LR1SV    | <8>     | On the rising edge of CLK at the end of the cycle in which this instruction is executing, the R1 register will be loaded with the data present on the SV port. The input to the Barrel Shifter will be passed onto the output unshifted.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LR2SV    | <9>     | On the rising edge of CLK at the end of the cycle in which this instruction is executing, the R2 register will be loaded with the data present on the SV port. The input to the Barrel Shifter will be passed onto the output unshifted.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ASRSV    | <a></a> | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number present in the SV register. The LSBs are discarded, and the vacant MSBs are filled with duplicates of the original MSB. (Sign Extension).                                                                                                                                                                                                                                                                                                                                                                                                      |

| ASRR1    | <b></b> | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number resident within the R1 register. The LSBs are discarded, and the vacant MSBs are filled with duplicates of the original MSB. (Sign Extension).                                                                                                                                                                                                                                                                                                                                                                                                 |

| ASRR2    | <c></c> | The 16 bit input to the Barrel Shifter is right shifted by the number of places indicated by the magnitude of the four bit number resident within the R2 register. The LSBs are discarded, and the vacant MSBs are filled with duplicates of the original MSB. (Sign Extension).                                                                                                                                                                                                                                                                                                                                                                                                 |

| NRMXX    | <d></d> | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number output from the Priority Encoder. This value is also output on the SV port (provided SVOE is low).  The effect of this operation is to left shift the input by the necessary amount (max 15 places) to result in the MSB and the next most significant bit being different. This has the effect of eliminating unnecessary Sign Bits, and hence Normalising the input data. The MSBs shifted out to the left are discarded, and the vacant LSBs on the right are filled with zeros.                                                             |

| NRMR1    | <e></e> | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number output from the Priority Encoder. This value is loaded into the R1 register at the end of the cycle, and is also output on the SV port (provided SVOE is low).  The effect of this operation is to left shift the input by the necessary amount (max 15 places) to result in the MSB and the next most significant bit being different. This has the effect of eliminating unnecessary Sign Bits, and hence Normalising the input data. The MSBs shifted out to the left are discarded, and the vacant LSBs on the right are filled with zeros. |

| NRMR2    | <f></f> | The 16 bit input to the Barrel Shifter is left shifted by the number of places indicated by the magnitude of the four bit number output from the Priority Encoder. This value is loaded into the R2 register at the end of the cycle, and also output on the SV port (provided SVOE is low).  The effect of this operation is to left shift the input by the necessary amount (max 15 places) to result in the MSB and the next most significant bit being different. This has the effect of eliminating unnecessary Sign Bits, and hence Normalising the input data. The MSBs shifted out to the left are discarded, and the vacant LSBs on the right are filled with zeros.    |

#### PDSP1601/1601A

#### **Barrel Shifter or ALU Register Instructions**

| Mnemonic | Op Code | Function                                                                                                                                                                                                                                                                                             |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LLRRR    | <0>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Right register will appear on the output. On the rising edge of CLK at the end of the cycle, the data on the register inputs will be loaded into the Left Register.            |

| LRRLR    | <1>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Left register will appear on the output. On the rising edge of CLK at the end of the cycle, the data on the register inputs will be loaded into the Right Register.            |

| LLRLR    | <2>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Left register will appear on the output. On the rising edge of CLK at the end of the cycle, the data on the register inputs will be loaded into the Left Register.             |

| LRRRR    | <3>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Right register will appear on the output. On the rising edge of CLK at the end of the cycle, the data on the register inputs will be loaded into the Right Register.           |

| LBRLR    | <4>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Left register will appear on the output. On the rising edge of CLK at the end of the cycle, the data on the register inputs will be loaded into both Left and Right Registers. |

| NOPRR    | <5>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Right register will appear on the output. On the rising edge ofd CLK at the end of the cycle no load operation will occur, the register contents will remain unchanged.        |

| NOPLR    | <6>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the contents of the Left register will appear on the output. On the rising edge of CLK at the end of the cycle no load operation will occur, the register contents will remain unchanged.          |

| NOPPS    | <7>     | After the rising edge of CLK at the beginning of the cycle in which this instruction is executed, the input to the registers will appear on the output. On the rising edge of CLK at the end of the cycle no load operation will occur, the register contents will remain unchanged.                 |

#### TYPICAL APPLICATION

Select a 16 bit field from each word in a block of 32 bit words with a 10MHz throughput.

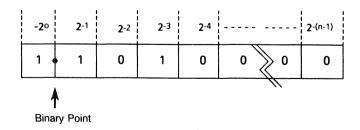

The 16 bit field indicated is to be selected from each 32 bit word.

The 32 bit words are fed into the B port of the PDSP1601 in two cycles. MS byte first.

The PDSP1601 shift control is initiated by programming the R1 and R2 registers with n and 16-n respectively.

The shift operation is implemented in three steps:-

(1) The MS byte is logically left shifted (16-n) places, the MSBs being discarded and the LSB spaces being filled with zeros. This shifted data is loaded into the shifter register file left register. (2) The LS byte is logically right shifted, n-places, the LSBs being discarded and the MSBs being filled with zeros. This shifted data is loaded into the shifter register file left register.

During this cycle the previous contents of this register are passed through the ALU to the ALU register file left register.

(3) While the MS byte of the next 32 bit word is shifted in the Barrel Shifter, the two previous results, resident within the left registers of the ALU and Shifter Register files are 'ORed' by the ALU, the result being the desired 16 bit field is loaded into the ALU register file right register ready to be output on the next cycle.

The instructions from initialisation are given in Table 6.

| CLK | CEB | MSA   | мѕв | MSS | MSC | IA    | IS    | sv     | RA    | RS    | Comment                                                     |

|-----|-----|-------|-----|-----|-----|-------|-------|--------|-------|-------|-------------------------------------------------------------|

| 1/  | 1   | MARSX | 1   | 0   | 0   | CLRXX | х     | х      | NOPLR | NOPLR | Clear                                                       |

| 2/  | 1   | MARSX | 1   | 0   | 0   | PASXA | LR1SV | · n    | NOPLR | NOPLR | Load R1 with n                                              |

| 3/  | 0   | MARSX | 1   | 0   | 0   | PASXA | LR2SV | (16-n) | NOPLR | NOPLR | Load R2 with (16-n)                                         |

| 4/  | 0   | MARSX | 1   | 0   | . 0 | PASXA | LSLR2 | Х      | NOPLR | LLRLR | Shift 1st MS byte                                           |

| 5/  | 0   | MARSX | 1   | 0   | 0   | PASXA | LSRR1 | Х      | LLRRR | LLRLR | Shift 1st LS byte                                           |

| 6/  | 0   | MARAX | 1   | 0   | 0   | ORXAB | LSLR2 | Х      | LRRLR | LLRLR | OR 1st bytes and                                            |

| 7/  | 0   | MARSX | 1 - | 0   | 0   | PASXA | LSRR1 | х      | LLRRR | LLRLR | shift 2nd MS byte Shift 2nd LS byte and output first result |

| 8/  | 0   | MARAX | 1   | 0   | 0   | ORXAB | LSLR2 | X      | LRRLR | LLRLR | Shift 3rd LS byte                                           |

Repeat instruction pair 5/ and 6/ until all 16 bit fields have been selected.

Table 6

1000mW

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

LC

| Supply Voltage Vcc                 | -0.5 to 7.0V      |

|------------------------------------|-------------------|

| Input Voltage Vin                  | -0.9 to Vcc +0.9V |

| Output Voltage Vout                | -0.9 to Vcc +0.9V |

| Clamp diode current per pin lk (Se | e Note 2) ±18mA   |

| Static discharge voltage (HMB)     | 500V              |

| Storage temperature Ts             | -65° C to +150° C |

| Ambient temperature with           |                   |

| power applied Tamb                 |                   |

| Military                           | -40°C to +125°C   |

| Industrial                         | -40 °C to +85 °C  |

| Package power dissipation PTOT     |                   |

| AC                                 | 1000mW            |

NOTES

Exceeding these ratings may cause permanent damage. Functional operation under these conditions is not implied.

Maximum dissipation or 1 second should not be exceeded, only

one output to be tested at any one time.

#### THERMAL CHARACTERISTICS

| Package type | θ <sub>JC</sub> °C/W | θ <sub>JA</sub> °C/W |

|--------------|----------------------|----------------------|

| LC           | 12                   | 35                   |

| AC           | 12                   | 36                   |

#### PDSP1601/1601A

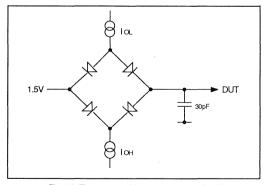

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb} \text{ (Industrial)} = -40 ^{\circ}\text{C to} + 85 ^{\circ}\text{C}, \ V_{CC} = 5.0 \text{V} \pm 10\%, \ \text{Ground} = 0 \text{V} \\ T_{amb} \text{ (Military)} = -55 ^{\circ}\text{C to} + 125 ^{\circ}\text{C}, \ V_{CC} = 5.0 \text{V} \pm 10\%, \ \text{Ground} = 0 \text{V}$

#### Static Characteristics

| Characteristic         | Cumphal | Value |                |     |       | 0                                                   |  |

|------------------------|---------|-------|----------------|-----|-------|-----------------------------------------------------|--|

| Characteristic         | Symbol  | Min.  | Min. Typ. Max. |     | Units | Conditions                                          |  |

| Output high voltage    | Vон     | 2.4   |                |     | V     | Iон = 8mA                                           |  |

| Output low voltage     | Vol     |       |                | 0.4 | l v   | IoL = -8mA                                          |  |

| Input high voltage     | ViH     | 2.0   |                |     | v     |                                                     |  |

| Input low voltage      | VIL     |       |                | 0.8 | V     |                                                     |  |

| Input leakage current  | lı∟     | -10   |                | +10 | μΑ    | GND < VIN < VCC                                     |  |

| Vcc current            | Icc     |       |                | 60  | mA    | $T_{amb} = -40^{\circ} C \text{ to } +85^{\circ} C$ |  |

| Output leakage current | loz     | -50   |                | +50 | μΑ    | GND < Vout < Vcc                                    |  |

| Output S/C current     | los     | 15    |                | 80  | mA    | Vcc = Max                                           |  |

| Input capacitance      | Cin     |       | 5              |     | pF    |                                                     |  |

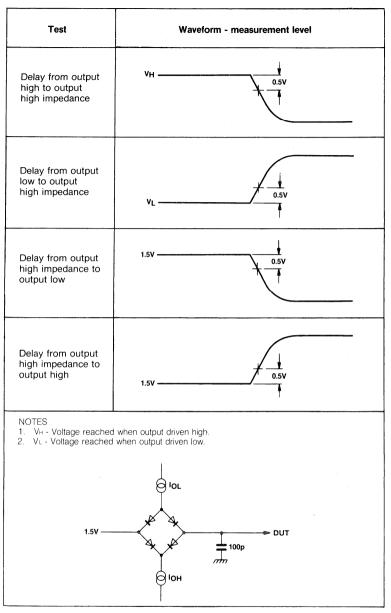

#### **Switching Characteristics**

|                                                                    |                    | Va   | lue   |       |            |                        |

|--------------------------------------------------------------------|--------------------|------|-------|-------|------------|------------------------|

| Characteristic                                                     | PDSP1601 PDSP1601A |      | 1601A | Units | Conditions |                        |

|                                                                    | Min.               | Max. | Min.  | Max.  |            |                        |

| CLK rising edge to C-PORT                                          | 5                  | 40   | 5     | 25    | ns         | 2× LSTTL + 20pF        |

| CLK rising edge to CO                                              | 5                  | 100  | 5     | 50    | ns         | 1× LSTTL+5pF           |

| CLK rising edge to BFP                                             | 5                  | 100  | 5     | 50    | ns         | 1× LSTTL+5pF           |

| Setup CEA or CEB to CLK rising edge                                | 30                 |      | 15    |       | ns         | · ·                    |

| Hold CEA or CEB to CLK rising edge                                 |                    | 0    |       | 0     | ns         |                        |

| Setup A or B port inputs to CLK rising edge                        | 40                 |      | 20    |       | ns         |                        |

| Hold A or B port inputs to CLK rising edge                         |                    | 0    |       | 0     | ns         |                        |

| Setup MSA0-1, MSB, MSS, MSC, RA2-0, RS0-2, IA0-4,                  | 40                 |      | 20    |       | ns         |                        |

| ISO-3, to CLK rising edge                                          |                    |      |       |       |            |                        |

| Hold RS0-2, IA0-4 to CLK rising edge                               |                    | 0    |       | 0     | ns         |                        |

| Hold IS0-3 to CLK rising edge                                      |                    | 3    |       | 3     | ns         |                        |

| Hold MSA0-1, MSB, MSS, MSC, RA0-2 to CLK rising edge               |                    | 0    |       | 0     | ns         |                        |

| Setup SV to CLK rising edge                                        | 40                 |      | 20    |       | ns         | Input mode             |

| Hold SV to CLK rising edge                                         |                    | 3    |       | 3     | ns         | Input mode             |

| CLK rising edge to SV                                              | 5                  | 100  | 5     | 50    | ns         | 20pF load, SV O/P mode |

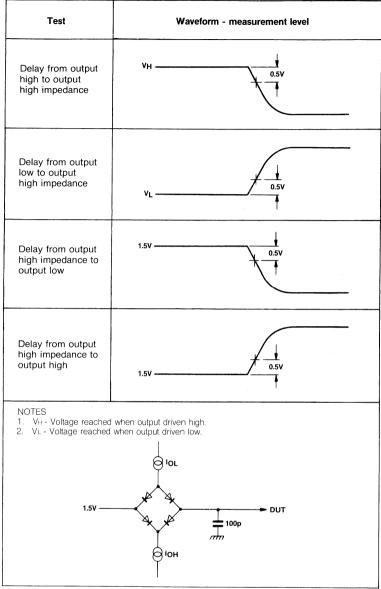

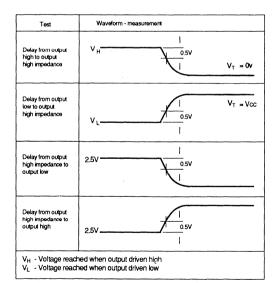

| OEC-PORT Z                                                         |                    | 40   |       | 25    | ns         | 2× LSTTL + 20pF        |

| OE _ C-PORT _ Z<br>OE _ C-PORT Z _                                 |                    | 40   |       | 25    | ns         | 2× LSTTL+20pF          |

| OEC-PORT Z                                                         |                    | 40   |       | 25    | ns         | 2× LSTTL + 20pF        |

|                                                                    |                    | 40   |       | 25    | ns         | 2× LSTTL + 20pF        |

| Clock period (ALU & Barrel Shifter, serial mode)                   | 200                |      | 100   |       | ns         |                        |

| Clock period (ALU & Barrel Shifter, parallel mode) Clock high time | 100                |      | 50    |       | ns         |                        |

| Clock low time                                                     | 40                 |      | 20    |       | ns         |                        |

| Olock low time                                                     | 40                 |      | 20    |       | ns         |                        |

#### ORDERING INFORMATION

Industrial

PDSP1601 B0 AC PDSP1601A B0 AC PDSP1601 B0 LC PDSP1601A B0 LC

Military

PDSP1601 A0 AC PDSP1601A0 LC

Call for availability on High Reliability parts and MIL-883C screening.

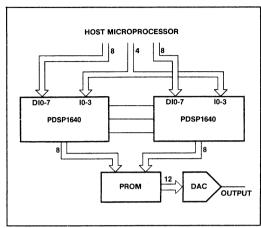

# PDSP1640 20MHz ADDRESS GENERATOR

The PDSP1640 is an 8-bit address generator which will cascade efficiently to wider address fields at very high speed, without the need for external carry logic.

Three PDSP1640s allow 24-bit addresses to be generated at up to 10MHz; four allow 32-bit addressing at up to 7MHz. A single PDSP1640 will address an 8-bit field at 20MHz.

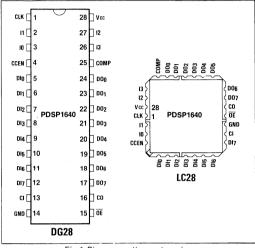

#### **FEATURES**

- 20MHz 8-Bit Address Generator

- Fast Cascade Logic gives 10MHz Operation at 24Bits

- Five On-chip User-Programmable Registers

- Output Mask Logic

- 300mW Maximum Power Dissipation

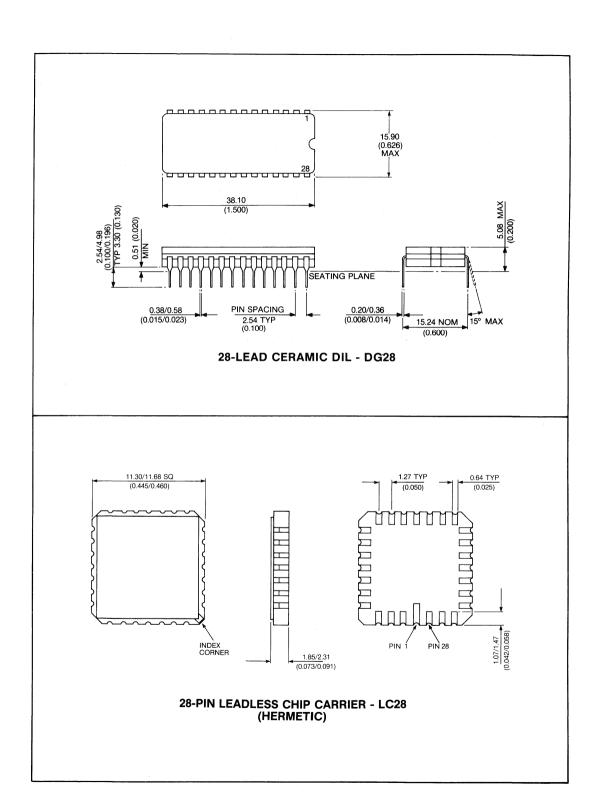

- 28-Pin DIL or LCC Package

#### **APPLICATIONS**

- DSP Address Generation

- Database Addressing

- DMA Controllers

- Modulo Counting

Fig.1 Pin connections - top view

#### ASSOCIATED PRODUCTS

PDSP16318 Complex Accumulator

PDSP16112 Complex Number Multiplier

PDSP1601 ALU and Barrel Shifter

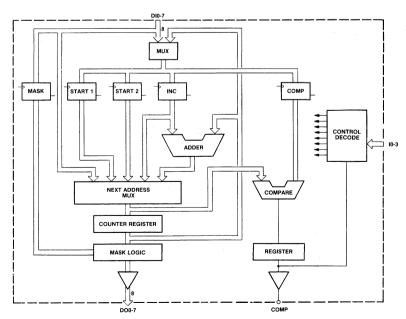

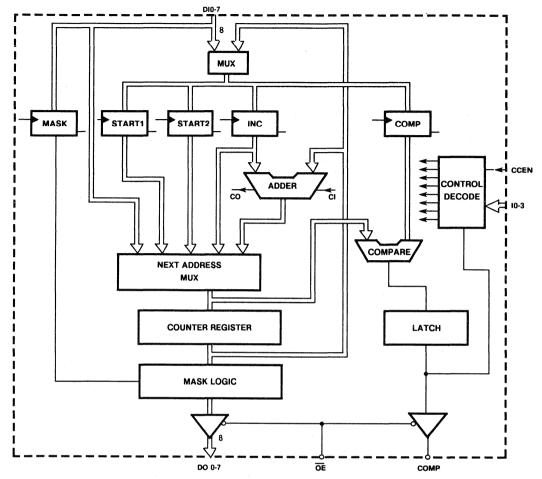

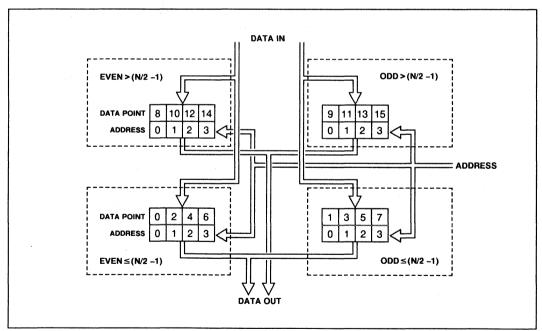

Fig.2 PDSP1640 simplified block diagram

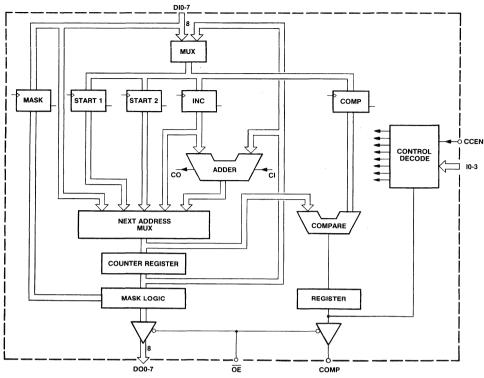

Fig.3 PDSP1640 block diagram

#### PIN DESCRIPTIONS

| Symbol | Pin No.       | Pin name and description                                                                                                                                                                                                                                                                                                                       |

|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

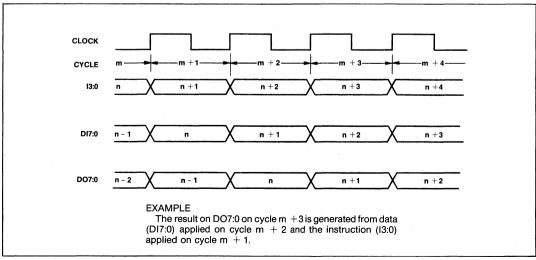

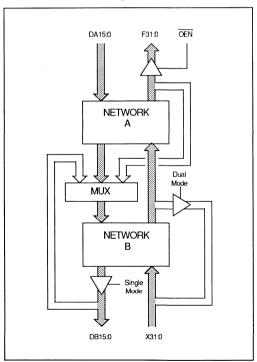

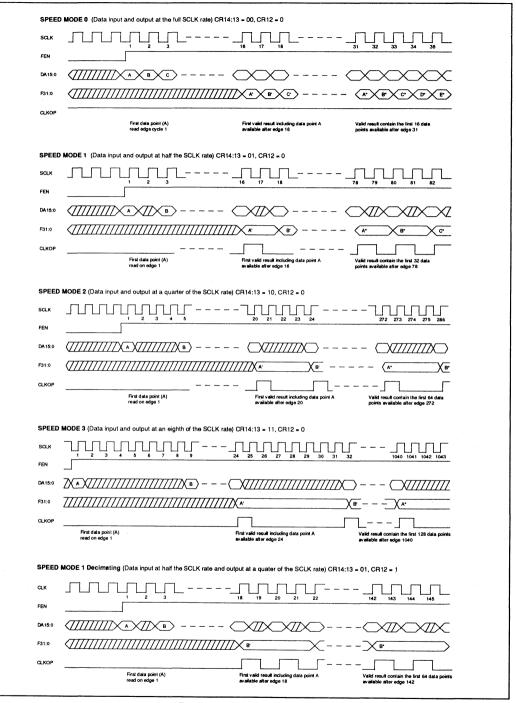

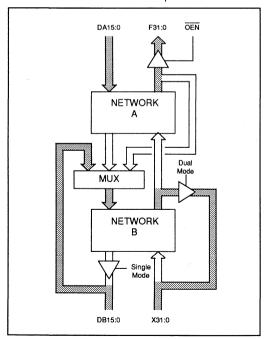

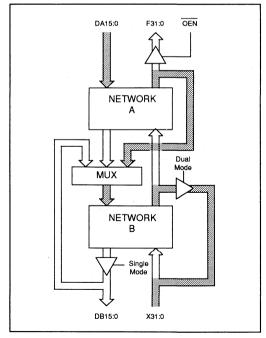

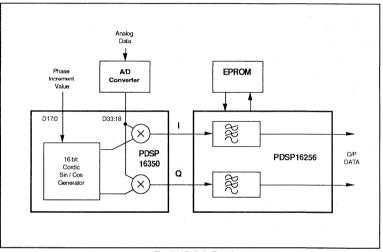

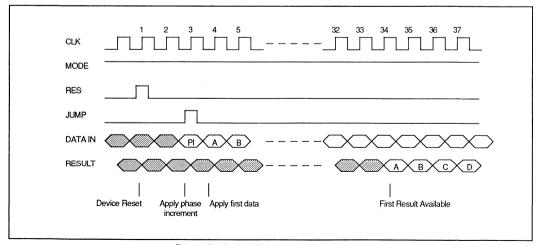

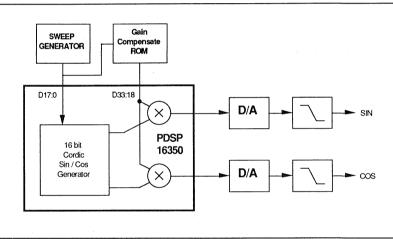

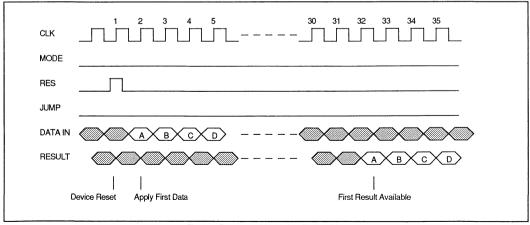

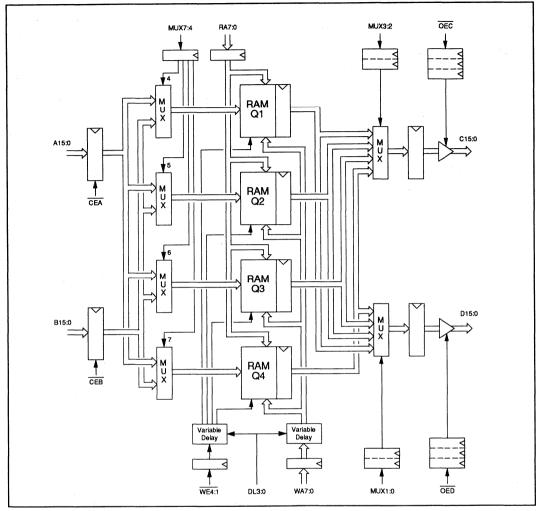

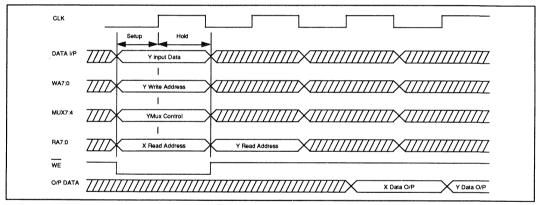

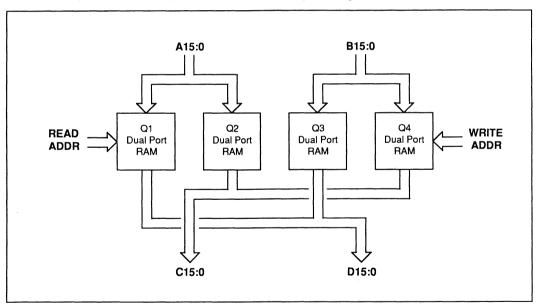

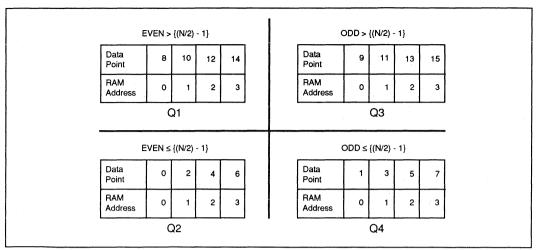

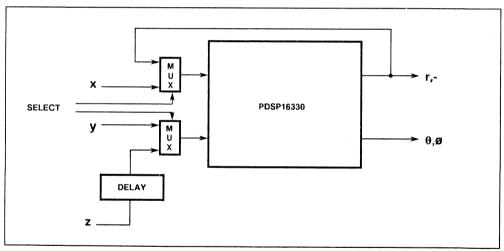

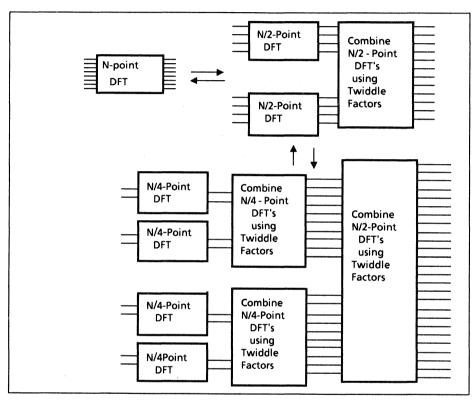

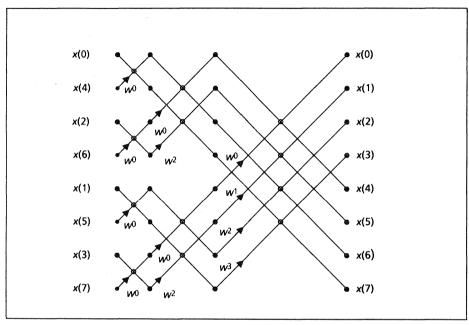

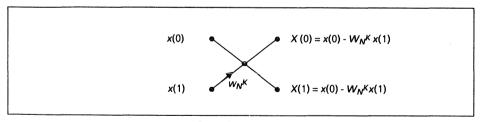

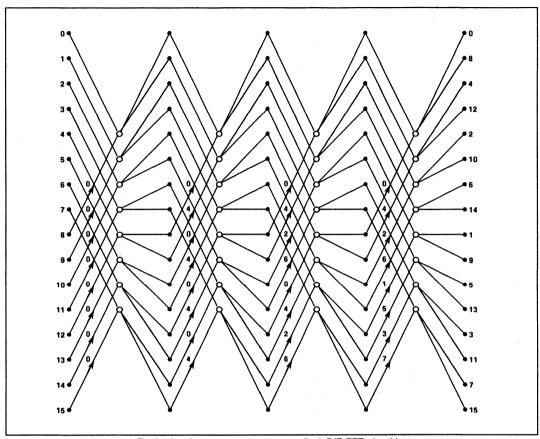

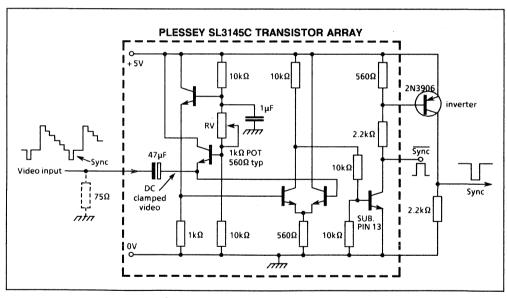

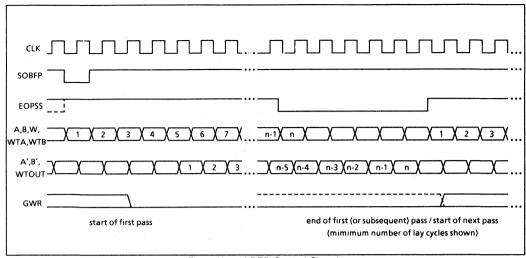

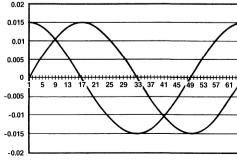

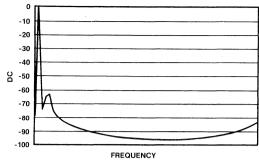

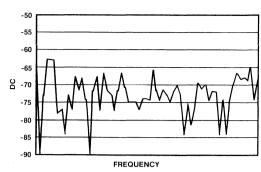

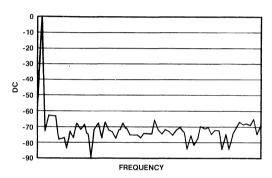

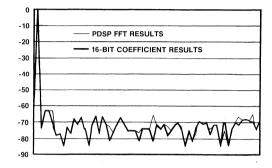

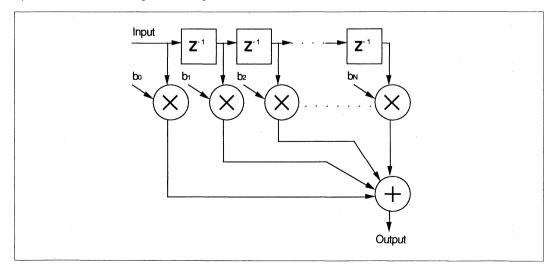

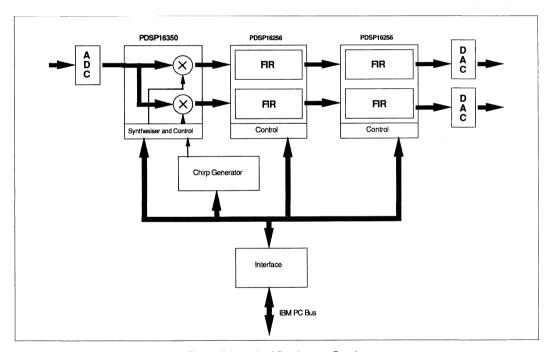

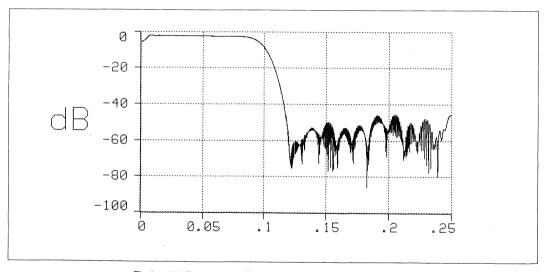

| CLK    | 1             | Common clock to all registered internal elements. All registers are loaded, and outputs change on the rising edge of CLK.                                                                                                                                                                                                                      |